|

|

Элементарные логические функции

Произвольная ПФ может быть выражена в форме функции от двоичных переменных (либо от других ПФ) с помощью ограниченного числа элементарных логических функций. Рассмотрим эти функции.

Логическое отрицание (функция НЕ). Логическим отрицанием переменной х называется такая ПФ f1(x), которая имеет значение 1, когда x = 0 и значение 0, когда х= 1. ПФ НЕ обозначается в виде Табл. 3.2 представляет собой таблицу истинности логической функции НЕ. Таблица 3.2

Функцию НЕ выполняет физический элемент (электронная схема), который называется элементом НЕ или инвертором. Обозначение инвертора на функциональных схемах показано на рис. 3.1.

Рис. 3.1.

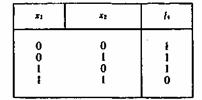

Логическое умножение (конъюнкция). Конъюнкция двух (или любого другого числа) переменных х1 и х2 принимает значение 1 только на наборе, в котором все переменные имеют значения 1. На остальных наборах эта функция имеет значение 0. Таблица 3.3

Табл. 3.3 представляет собой таблицу истинности конъюнкции двух переменных х1 и x2. ПФ конъюнкция обозначается в виде

и читается: «f2 есть (эквивалентно) х1 и x2».

Рис. 3.2. Для обозначения конъюнкции можно использовать символы Функция И выполняется электронной схемой, которая называется элементом И или коньюнктором. Обозначение элемента И на функциональных схемах показано на рис. 3.2. Число входов элемента И равно числу переменных, участвующих в операции умножения.

Логическое сложение (дизъюнкция). Дизъюнкция двух (или любого другого числа) переменных х1 и х2 имеет значение 0 только на наборе, в котором все переменные имеют значение 0. Если хотя бы одна из переменных равна 1, функция будет иметь значение 1. Табл. 3.4 есть таблица истинности для дизъюнкции двух переменных х1 и х2. ПФ дизъюнкция записывается в виде

и читается: «f3 есть (эквивалентно) х1 или x2». Кроме символа + , для дизъюнкции употребляется символ V. Так как функция дизъюнкции имеет значение 1, если первый или второй аргументы имеют значение 1, операция дизъюнкции называется также операцией ИЛИ. Таблица 3.4

Операция ИЛИ реализуется электронной схемой, которая называется элементом ИЛИ или дизъюнктором. Обозначение элемента ИЛИ на функциональных схемах показано на рис. 3.3. Число входов элемента ИЛИ равно числу переменных, участвующих в операции дизъюнкции.

Рис.3.3. Элементарные логические функции НЕ, И, ИЛИ являются основными логическими функциями. Имеется еще несколько логических функций, производных от основных функций (т. е. выражающихся через функции НЕ, И, ИЛИ), которые реализуются соответствующими электронными элементами и так часто встречаются в схемотехнике ЭВМ, что им были даны собственные названия. Рассмотрим эти функции.

Отрицание конъюнкции (операция И — НЕ). Эта функция образуется путем отрицания результата, получаемого при выполнении операции И. Табл. 3.5 есть таблица истинности операции И — НЕ для двух переменных. Из сравнения табл. 3.3 и 3.5 видно, что ПФ И — НЕ является отрицанием (операцией НЕ) конъюнкции. ПФ И — НЕ записывается в виде

Таблица 3.5.

Функцию И — НЕ выполняет схема, которая называется элементом И — НЕ. Обозначение элемента И — НЕ на функциональных схемах показано на рис. 3.4. Число входов элемента И — НЕ определяется числом аргументов функции И — НЕ.

Рис. 3.4.

Отрицание дизъюнкции (операция ИЛИ — НЕ). Эта операция образуется путем отрицания результата, полученного при выполнении операции ИЛИ. Табл. 3.6 Таблица 3.6

представляет собой таблицу истинности операции ИЛИ — НЕ для двух переменных. Из сравнения табл. 3.4 и 3.6 видно, что ПФ ИЛИ — НЕ является отрицанием (операцией НЕ) дизъюнкции. ПФ ИЛИ — НЕ записывается в виде

Операцию ИЛИ — НЕ выполняет электронный элемент, который называется элементом ИЛИ — НЕ. Обозначение элемента ИЛИ — НЕ на функциональных схемах показано на рис. 3.5. Число входов элемента ИЛИ — НЕ определяется числом аргументов функции ИЛИ — НЕ.

Рис.3.5.

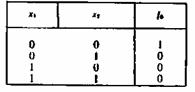

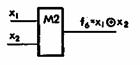

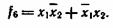

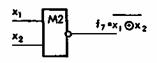

ИСКЛЮЧАЮЩЕЕ ИЛИ (операция НЕРАВНОЗНАЧНОСТЬ или СЛОЖЕНИЕ ПО МОДУЛЮ ДВА). Данная функция имеет значение 1 на тех наборах переменных, в которых число единиц нечетно. Для двух переменных операция НЕРАВНОЗНАЧНОСТЬ иллюстрируется таблицей истинности (табл. 3.7). Эта операция записывается для двух переменных в виде

Условное обозначение элемента, выполняющего функцию НЕРАВНОЗНАЧНОСТЬ, на функциональных схемах приведено на рис. 3.6. Символ М2 в поле элемента означает «сложение по модулю два».

Рис.3.6. Операция НЕРАВНОЗНАЧНОСТЬ выражается через операции НЕ, И, ИЛИ в виде

Таблица .3.7.

Операция ИСКЛЮЧАЮЩЕЕ ИЛИ — НЕ (РАВНОЗНАЧНОСТЬ). Функция РАВНОЗНАЧНОСТЬ представляет собой отрицание операции ИСКЛЮЧАЮЩЕЕ ИЛИ. Данная операция имеет значение 1 на тех наборах переменных, которые содержат четное число единиц. Для двух переменных операция ИСКЛЮЧАЮЩЕЕ ИЛИ — НЕ представлена таблицей истинности (табл. 3.8). Эта операция записывается для двух переменных в виде

Таблица 3.8.

Операция ИСКЛЮЧАЮЩЕЕ ИЛИ — НЕ выражается через операции НЕ, И, ИЛИ в виде

Функцию РАВНОЗНАЧНОСТЬ выполняет электронный элемент с аналогичным названием, изображение которого на функциональных схемах дано на рис. 3.7.

7. Базовые элементы ЭВМ Общие сведения.

Схемотехника — научно-техническое направление, занимающееся проблемами анализа и синтеза отдельных приборов радиотехники, связи, автоматики, вычислительной техники с целью обеспечения оптимального выполнения ими заданных функций и расчета параметров входящих в них элементов. Элементами электронных вычислительных машин называются наименьшие функциональные части, на которые можно разделить машину при ее логическом проектировании и технической реализации. Элементы ЭВМ выполняют хранение, преобразование и передачу двоичных переменных, а также ряд вспомогательных функций: задержку сигнала во времени, формирование сигнала с определенными физическими характеристиками и т. п. Основу элементной базы ЭВМ составляют цифровые интегральные схемы (ИС). Их сложность характеризуется степенью функциональной интеграции Ки (Ки= lg Nэл где Nэл —число элементов И — НЕ либо ИЛИ — НЕ, расположенных на кристалле ИС). В зависимости от сложности интегральные схемы подразделяются на следующие типы: МИС — малые интегральные схемы, содержащие один или несколько логических элементов (Ки ≈1); СИС — средние интегральные схемы, содержащие один или несколько функциональных узлов (сумматоров, счетчиков и др.) и имеющие обычно Ки = 1...2; БИС — большие интегральные схемы, содержащие одно или несколько функциональных устройств (арифметическое устройство, арифметико-логическое устройство АЛУ, устройство управления УУ, запоминающее устройство ЗУ) и имеющие Ки = 2 - 4; СБИС — сверхбольшие БИС, выполняющие функции целых цифровых систем (например, микроЭВМ) и имеющие Ки > 4. По типу обрабатываемых сигналов элементы ЭВМ подразделяются на потенциальные, импульсные и импульс но-потенциальные. Длительность потенциального сигнала не ограничена сверху, как правило, кратна длительности такта Т и определяется частотой смены информации.

Рис. 4.1 Длительность импульсного сигнала имеет некоторое постоянное стандартное значение tи < Т и но .не зависит от частоты смены информации. Типы сигналов определяют три способа представления (кодирования) информации: потенциальный (рис. 4.1, а), импульсный (рис. 4.1. б) и динамический (рис. 4.1, в). По функциональному назначению элементы делятся на логические, элементы памяти и специальные. К логическим относят элементы, реализующие функции из базисной системы (базисную функцию). Элементы памяти (триггеры) предназначены для запоминания (храпения) информации, а специальные элементы — для физического преобразования электрических сигналов, т. е. усиления, формирования, генерирования, задержки и т. п.

10. Организация микропроцессора Перечислим основные функции микропроцессора: • выборка команд из ОЗУ; •декодирование команд (т.е. определение назначения команды, способа ее исполнения и адресов операндов); • выполнение операций, закодированных в командах; • управление пересылкой информации между своими внутренними регистрами, оперативной памятью и внешними (периферийными) устройствами; • обработка внутрипроцессорных и программных прерываний; • обработка сигналов от внешних устройств и реализация соответствующих прерываний; • управление различными устройствами, входящими в состав компьютера. Внутреннее устройство микропроцессоров очень сложно (вспомним три миллиона транзисторов в «Pentium»). Даже если попытаться рассмотреть наиболее общую схему основных функциональных узлов, и то получится достаточно сложная картина. К тому же внутреннее устройство МП сильно зависит от его марки, а стало быть изучение структуры одного процессора не обязательно помогает понять работу другого. Следует признать нецелесообразным для пользователя (и даже, может быть, для программиста) изучение инженерных деталей процессора современной ЭВМ, и ограничиться, как это принято делать, только теми функциональными узлами, которые доступны программно. При таком подходе оказывается, что МП имеют много общего, и становятся отчетливо видны некоторые закономерности их внутреннего устройства. Кроме того, исчезает пугающая сложность и возникает приятное и полезное чувство, что компьютер - это не какая-то там «вещь в себе» и его поведение можно понять. Итак, что же представляет собой микропроцессор с точки зрения программиста? Рассмотрение начнем в наиболее общем виде, не конкретизируя пока тип МП. Ответ на поставленный вопрос, как ни странно, будет чрезвычайно прост: для программиста любой процессор состоит из набора регистров памяти различного назначения, которые определенным образом связаны между собой и обрабатываются в соответствии с некоторой системой правил. Конечно, программисту доступна не вся внутренняя память процессора: есть множество рабочих (программно-недоступных) регистров, использующихся только во время выполнения команд и т.п.; их мы рассматривать не будем. Обсуждение внутренних регистров микропроцессора начнем с наиболее важных: счетчика адреса команд, указателя стека и регистра состояния. Наличие счетчика адреса команд, как уже говорилось выше, было предложено еще в работахфонНеймана. Роль счетчика состоит в сохранении адреса очередной команды программы и автоматическом вычислении адреса следующей. Благодаря наличию программного счетчика в ЭВМ реализуется основной цикл исполнения последовательно расположенных команд программы. Заметим, что не во всех МП счетчик команд программно доступен.

Наконец, регистр состояния процессора. Для разных МП он может называться по-разному (например, слово состояния процессора, регистр флагов и т.п.), но суть его всегда одна: в этом регистре хранятся сведения о текущих режимах работы процессора. Сюда же помещается информация о результатах выполняемых команд, например, равен ли результат нулю, отрицателен ли он, не возникли ли ошибки в ходе операции и т.п. Использование и анализ информации в этом очень важном регистре происходит побитно; иными словами, каждый бит регистра состояния имеет самостоятельное значение. Содержание регистра состояния МП всегда старается сохранить в первою очередь сразу после значения командного счетчика. Помимо рассмотренных выше, каждый МП имеет набор рабочих регистров, в которых хранятся текущие обрабатываемые данные или их адреса в ОЗУ. У некоторых процессоров регистры функционально равнозначны (классическим примером служит процессор машин семейства PDP). в других (к ним принадлежит все интел-ловское семейство МП) назначение регистров достаточно жестко оговаривается. В последнем случае выделяется особый регистр, который принято называть аккумулятором.. В нем производятся все основные операции и сохраняется их результат Завершая разговор о регистрах, укажем на существование определенных связей между ними: информация из одного может передаваться в другой. Для машин с равноправными регистрами передача данных возможна между любыми регистрами, для остальных - между строго определенными парами. Так или иначе (в худшем случае за несколько машинных команд) информациюиз одного регистра МП всегда можно перенести в другой. Разрядность регистров МП существенно влияет на возможности всей ЭВМ. Поэтому уточним понятие «разрядность ЭВМ». Оно включает • разрядность внутренних регистров микропроцессора(m); • разрядность шины данных (n); • разрядность шины адреса(k).

Рис. 4.12. Обмен информацией между процессором и основной памятью

Схема обмена информацией между микропроцессором и ОЗУ представлена на рис. 4.12. Данные поступают из ОЗУ в регистры процессора и наоборот по шине данных; по шине адреса передается информация о месте хранения данных в ОЗУ. Разрядности этих шин могут не совпадать: например, упомянутый выше МП «Intel 8088» характеризовался значениями m/n/k = 16/8/20. Когда говорят, не вникая в детали, «16-разрядная ЭВМ», то имеют в виду значение т. Поскольку объем адресного пространства ОЗУ, контролируемого МП, равен 2k, то понятно стремление увеличить разрядность шины адреса.

12.Блок регистров общего назначения Как уже отмечалось, вычислительные ресурсы МП во многом определяются числом, составом и назначением регистров блока РОН. Обычно этот блок содержит от 4 до 16 регистров. Рассмотрим распределение функций между этими регистрами и способы их использования в МП - системах. В общем случае регистры МП служат для хранения операндов, промежуточных результатов, для формирования адресов, а в некоторых МП — и в качестве внутреннего регистрового стека. Сложности проектирования МП - систем, порождаемые малым числом регистров общего назначения, преодолеваются путем использования в блоке РОН специализированных регистров, т. е. регистров, выполняющих ограниченные функции. В результате упрощается аппаратная реализации этих регистров, но возникает необходимость в специфических приемах программирования, присущих только данному МП. Таким специализированным регистром в блоке регистров является счетчик команд PC, содержащий адрес ячейки памяти, из которой выбирается следующая команда. Во время выборки команды содержимое счетчика PC передается в регистр адреса и из него поступает в шину адреса. Под воздействием управляющего автомата МП содержимое счетчика команд увеличивается на 1 для указания адреса следующей команды. Для неветвящегося процесса по окончании выполнения текущей команды МП готов к выбору очередной команды из программы. При переходе по программе к другому адресу этот альтернативный адрес передачи укрепления загружается в счетчик команд PС. Как привило, переходы по программе происходят под управлением программы, но во время процедур ввода-вывода адрес передачи управления на счетчике команд PC может быть задан внешним устройством. Для реализации методов непрямой адресации команд и данных в составе блока регистров МП выделяются специальные регистры, назначение которых — указывать адреса ячеек, где хранятся операнды, что позволяет иметь в команде ограниченное число разрядов, необходимое только для указаний этих специальных регистров. Именно этим объясняется наличие в составе блока РОН МП таких регистров, как регистр косвенного адреса (HL) и регистр-указатель стека SP. В некоторых МП, кроме того, имеется регистр XR. В стеке, который оперирует со связанными списками данных, также реализуется подразумеваемая адресация, так как стек имеет определенную дисциплину доступа (LIFO). Использование стека весьма эффективно при обработке связанных структур данных, а также данных с многоуровневыми вложениями. Каждое обращение к стеку для занесения в него слова сопровождается автоматическим добавлением 1 к содержимому регистра указателя стека SP, а каждое обращение к стеку для извлечения слова сопровождается автоматическим выполнением операции уменьшения содержимого SP на 1. Содержимое SP указывает на верхний элемент списка данных, тем самым реализуя неявное задание относительного расположения элементов всего списка. В силу того что по технологическим причинам поместить на кристалле МП блок регистров с дисциплиной доступа LIFO не всегда возможно, стек, как правило, реализуется во внешней интегральной памяти. Такое размещение стека вне МП оправдано двумя обстоятельствами: 1) обращение к стеку производится много реже, чем обращение к внутренним регистрам; 2) при размещении стека во внешней памяти практически неограниченно возрастает число уровней вложения в стеке. Вся емкость внешней памяти может адресоваться регистром-указателем стека SP, что при 16-разрядной адресной шине дает возможность создать стек глубиной 64 К. В составе блока РОН микропроцессора имеется специальный регистр-указатель стека SP. Особенностью блока РОН микропроцессора является наличие в его составе схемы инкрементора/декрементора (INС/DEC), которая позволяет производить операции автоадресации с приращением (+/-) непосредственно в блоке РОН при обработке адресов, команд и данных, что освобождает АЛУ от выполнения операций над адресами. Схема инкрементора/декрементора, реализованная в виде достаточно простой комбинационной схемы, выполняет операции INC и DEC в процессе межрегистровых пересылок. Использование этой специализированной схемы инкрементора/декрементора в блоке РОН позволяет реализовать процедуры автоматического задания приращений в МП-системе при операциях с адресами не только в регистре-указателе стека, но и в счетчике команд, в индексном регистре, в регистре косвенного адреса и т.д. При выполнении операций в МП-системах возникает потребность в кратковременном хранении некоторых операндов и результатов выполнения операций. Для этой цели в блоке РОН или вне его имеется некоторое число регистров временного хранения данных TEMP (temporary registers). Использование регистров временного хранения информации позволяет МП за один цикл выполнения команды реализовать, например, такую операцию, как обмен содержимым двух регистров, принадлежащих блоку РОН. Буферные регистры временного хранения данных TEMP построены по простейшему принципу динамического хранения переменных на емкостях затворов МОП-транзисторов. Они позволяют простейшими аппаратными средствами выполнять довольно сложные операции «перетасовки» данных не только между регистрами блока РОН, но и между регистрами, аккумулятором и внешней памятью. Характерной для блока РОН микропроцессора особенностью является использование принципа тандемных пересылок при операциях с адресами. Суть его заключается в следующем. Так как шина данных МП всего лишь 8-разрядная, то все регистры, имеющие собственные символьные имена, представляют собой 8-разрядные регистры (за исключением программного счетчика и указателя стека). Поэтому при формировании адреса (а разрядность адресной шины равна 16) возникает необходимость рассматривать содержимое некоторых пар регистров как одно слово удвоенной разрядности, т. е. возникает необходимость автоматически выполнять в МП операцию конкатенации над содержимым пары регистров. Следовательно, внутренняя структура блока РОН должна иметь такую организацию, которая допускает одновременные пересылки внутри блока двух байтов информации. С другой стороны, принцип тандемных пересылок используется на этапе загрузки МП данными из памяти или внешних устройств. При использовании трехбайтных команд первый байт команды всегда поступает на регистр команды IR. Дешифратор команды, принадлежащий управляющему автомату, выделяет из кода команды признак, указывающий на то, что данная команда трехбайтная. В результате управляющий автомат последовательно генерирует две связанные пары сигналов. Первый сигнал в каждой паре выполняет операцию INC PC, т. е. увеличивает на 1 содержимое программного счетчика с тем, чтобы обеспечить выборку двух остальных байтов трехбайтной команды, а вторые сигналы в этой паре представляют собой сигналы LOAD RP, т. е. сигналы загрузки связанной пары регистров. Примером таких тандемных пересылок может служить процедура реализации команды LHLD, т. е. команды загрузки регистров Н и L МП 8080 с прямой адресацией. И, наконец, в состав блока РОН входит регистр-защелка адреса ADDRESS LATCH. Собственно регистр адреса недоступен программисту. Однако любая пара регистров (WZ, BC, DE, HL) может быть использована для задания адресов команд и данных в программе. Этот адрес может под воздействием соответствующих команд не только быть загруженным в регистр-защелку адреса, но и модифицирован (INC/DEC) в процессе загрузки. Регистр-защелка адреса передает адрес в буферную схему и далее в шину адреса АВ.

14. Архитектура однокристального микропроцессора 8080 8080 является однокристальным микропроцессором, работающим с 8-разрядной шиной данных и 16-разрядной шиной адреса. Управляющие сигналы передаются по шине управления. Шины отделены друг от друга. Структура Intel 8080 приведена на рис. 1.

Микропроцессор содержит внутреннюю шину данных, посредством которой происходит обмен информацией между внутренними регистрами, арифметико-логическим устройством, обрабатывающим 8-разрядные данные и передающим их через буфер на внешнюю шину данных. Кроме того, в состав 8080 входит устройство управления, буфер адресной шины, связанный с регистром команд и блок регистров. В общих чертах работа микропроцессора выглядит следующим образом: в регистре, называемом программным счетчиком, хранится адрес следующей команды, которую необходимо выполнить. Устройство управления подключает этот регистр к шине адреса (конечно, через буфер) и выдает управляющие сигналы, необходимые для чтения кода команды из памяти. На этом завершается первый такт. В следующем такте микропроцессор проверяет состояние сигналов на входе готовности и запрос останова. При их наличии микропроцессор переходит в соответствующее состояние. В противном случае, после появления на шине управления сигналов, подтверждающих выдачу кода команды на шину данных, устройство управления подключает к ней регистр команды и записывает в нее полученный код. Это требуется потому, что команда передается только в первом машинном цикле, а сохранить ее нужно на все время выполнения команды. Из регистра команды ее код поступает в дешифратор команды и затем в устройство управления, которое в зависимости от поступившей команды либо сразу переходит к ее выполнению, либо считывает данные или адрес, расположенные сразу после кода команды и необходимые для ее выполнения. На это тратится третий такт и, если это необходимо, четвертый и пятый такты. Таким образом, вся команда выполняется за 3-5 тактов. При тактовой частоте 2 МГц это составляет 1.5-2.5 мкс. Перед выполнением команды проверяется состояние сигнала на входе захвата шины HLD (этот сигнал отключает микропроцессор от шины, давая внешним устройствам возможность прямого доступа в память по общей шине). При его обнаружении микропроцессор переходит в состояние захвата и вырабатывает сигнал подтверждения захвата шины. После снятия сигнала HLD процессор продолжает выполнение команды. В конце машинного цикла вновь анализируется состояние входа захвата, а затем проверяется, завершено ли выполнение команды. Если нет, то микропроцессор переходит к выполнению следующего цикла команды. Это может быть цикл работы с оперативной памятью или с внешним устройством. После выполнения каждой команды проверяется состояние входа запроса прерывания. Если этот сигнал присутствует, то текущая программа приостанавливается и на шину данных выдается сигнал "подтверждение прерывания". Затем внешний контроллер прерываний передает по шине данных команду и адрес перехода к подпрограмме обработки прерывания. По окончании обработки прерывания происходит возврат к выполнению прерванной программы. Сигнал готовности позволяет синхронизировать работу микропроцессора с работой более медленных устройств, и, кроме того, используется для пошагового выполнения программ. Следующим важным узлом микропроцессора является блок регистров. Он включает в себя 16-разрядный регистр для временного хранения данных WZ, шесть 8-разрядных регистров общего назначения B, C, D, E, H, L, которые могут использоваться парами в качестве 16-разрядных — BC, DE, HL (это сделано прежде всего для удобной работы с адресами). Кроме того, блок регистров содержит 16-разрядный регистр адреса команды IP (программный счетчик), 16-разрядный регистр указателя стека SP, а также 16-разрядную схему инкремента-декремента. С помощью последней изменяется, например, состояние программного счетчика после выполнения каждой следующей команды. Еще один важный узел — регистр результата (аккумулятор), связанный с АЛУ и используемый для хранения одного из исходных операндов или результата выполнения команды. Последний регистр — это регистр флажков. В нем записан байт, каждый бит которого содержит информацию о результате выполнения последней команды.

16.Законы Булевой алгебры В булевой алгебре используются четыре основных закона: переместительный, сочетательный, распределительный, инверсии. Эти законы позволяют проводить эквивалентные преобразования ПФ, записанных с помощью операций НЕ, И, ИЛИ, т. е. приводить выражения ПФ к удобному (более простому) виду. Рассмотрим эти законы.

Переместительный закон аналогичен переместительному закону обычной алгебры и записывается в виде: а) для дизъюнкции

б) для конъюнкции

Таким образом, от перемены мест слагаемых (сомножителей) их логическая сумма (логическое произведение) не меняется.

Сочетательный закон также аналогичен сочетательному закону обычной алгебры и записывается в виде: а) для дизъюнкции

б) для конъюнкции

Следовательно, можно группировать переменные, объединенные знаком дизъюнкции или конъюнкции, это не меняет значений ПФ.

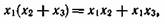

Распределительный закон записывается в виде: а) для дизъюнкции

т. е. дизъюнкция переменной и конъюнкции равносильна конъюнкции дизъюнкций этой переменной с сомножителями; б) для конъюнкции

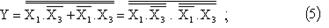

т. е. конъюнкция переменной и дизъюнкции эквивалентна дизъюнкции конъюнкций этой переменной со слагаемыми. Справедливость выражения (3.5) доказывается путем г составления таблиц истинности для левой и правой частей. Значения этих таблиц совпадают для одинаковых наборов переменных, это и доказывает справедливость (3.5).

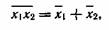

Закон инверсии: а) для дизъюнкции

т. е. отрицание дизъюнкции логических переменных эквивалентно конъюнкции отрицаний этих переменных; б) для конъюнкции

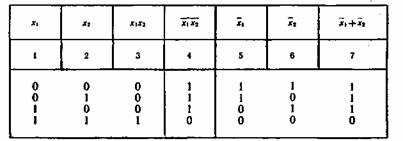

т. е. отрицание конъюнкции переменных эквивалентно дизъюнкции отрицаний этих переменных. Справедливость выражений (3.7) и (3.8), как и (3.5), докалывается также путем составления таблиц истинности для левой и правой частей каждого выражения и их сравнения на совпадение для одних и тех же наборов переменных. Докажем, например, справедливость формулы (3.8). Для этого составим таблицу истинности (табл. 3.9) правой и левой части соотношения (3.8). Из табл. 3.9 видно, что содержимое столбцов 4 и 7 совпадает на одних и тех же наборах переменных (т. е. в одних и тех же строках). Это и доказывает справедливость формулы (3.8). Из законов алгебры логики выводится ряд важных правил, которые полезны при выполнении эквивалентных преобразований ПФ.

1. Выражения, имеющие всегда значение 1:

2.Выражения, имеющие всегда значение 0:

3. Двойное отрицание: 4.Повторение:

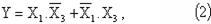

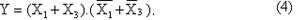

5.Склеивание: Это правило доказывается путем вынесения в левой части х1 за скобку и применения правила 1 для выражения, имеющего значение 1: 6.Поглощение: Для доказательства справедливости этого правила вынесем в левой части за скобку х1 и применим правило 1 для выражения, имеющего значение 1: 18.Синтез переключательной функций Любая логическая функция может быть представлена в дизъюнктивной или конъюнктивной нормальной форме (ДНФ или КНФ). ДНФ представляет собой логическую сумму элементарных произведений, каждое из которых аргумент или его отрицание входит не более одного раза. Если каждое слагаемое содержит все переменные или их отрицания, то имеет стандартную форму (СДНФ): совершенную дизъюнктивную нормальную форму (СДНФ), которая является одним из вариантов алгебраического способа задания булевых функций. Синтез переключательной функции состоит в получении ее ДНФ или КНФ и получении минимальной формы функций. При синтезе схем выполняется задача построения схем с использованием минимального числа элементов в базисе И-НЕ или ИЛИ-НЕ. Синтез комбинационных схем с одним выходом осуществляется в следующей последовательности. На первом этапе осуществляется запись условий функционирования в виде логической функции, словесно в виде таблиц истинности, структурных формул. На втором этапе осуществляется запись и минимизация структурной формулы, т.е. осуществляется приведение переключательной функции к совершенной нормальной форме и ее минимизация. На третьем этапе осуществляется запись минимизированной структурной формулы на заданном базисе. Чаще всего в универсальных базисах И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ. На четвертом этапе составляется структурная схема, определяющая число элементов и необходимые соединения между ними. Рассмотрим пример синтеза комбинационной схемы. Пусть заданы условия функционирования в виде таблицы истинности (табл. 2, вариант 13). Записываем структурную формулу в виде СДНФ по таблице истинности

Число слагаемых определяется числом единичных наборов (Y = 1) таблицы истинности, а число сомножителей определяется числом независимых переменных, входящих в рассматриваемые наборы. Для реализации этой функции необходимо иметь 4 трехвходовых элемента И и один четырехвходовый элемент ИЛИ. Минимизацию структурной формулы (1) произведем при помощи диаграммы Вейча (рис. 9). Получаем выражение

которое также можно получить, применив правило склеивания,

Полученную минимизированную структурную формулу можно также представить в виде

Производим преобразования структурных формул (2) и (4) в базисе И-НЕ, используя законы инверсии (формулы де Моргана):

Структурные схемы, составленные по формулам (2), (5) и (6), приведены на рис. 10. Видим, что после минимизации для реализации функции требуется меньшее число логических элементов.

Рис. 9. Минимизация переключательной функции при помощи диаграмм Вейча

Рис. 10. Примеры реализации минимизированной функции согласно выражениям (2), (5), (6)

19. Системы прерываний Прерывание - приостановление работы одной программы и передача управления другой при возникновении некоторого независящего от них события. При этом сохраняется возможность возврата управления прерванной программе, без потери ею работоспосодности. Адреса подпрограмм обслуживания прерываний находятся в специальной таблице и называются векторами прерывания. В реальном режиме таблица вектров распологается в начале физической памяти; вектор имеет длину четыре байта и храниться в форме CS:IP. В защищенном режиме таблица векторов может быть расположена в любом месте и содержит более сложные дескрипторы (в режиме V86 имеется подобие таблицы реального режима). Работа с системой прерываний может рассматриваться с двух точек зрения: 1. Работа с векторами прерываний; 2. Работа с микросхемами контроллеров прерываний (современные рашины могут не иметь отдельной микросхемы контроллера прерываний, но их регистры сохранены в адресном пространстве). При работе в режиме V86 возможно изменение образа таблицы прерываний, но последствия определяются возможностями виртуального монитора!

Не нашли, что искали? Воспользуйтесь поиском по сайту: ©2015 - 2026 stydopedia.ru Все материалы защищены законодательством РФ.

|

и читается: «f1 есть (эквивалентно) не х».

и читается: «f1 есть (эквивалентно) не х».

или &. Конъюнкция называется также функцией И, так как она имеет значение 1, только если первый и второй аргументы имеют значения 1.

или &. Конъюнкция называется также функцией И, так как она имеет значение 1, только если первый и второй аргументы имеют значения 1.

Рис.1. Внутренняя структура микропроцессора 8080. Увеличить рисунок

Рис.1. Внутренняя структура микропроцессора 8080. Увеличить рисунок (3.1)

(3.1) (3.2)

(3.2) (3.3)

(3.3) (3.4)

(3.4) (3.5)

(3.5) (3.6)

(3.6) (3.7)

(3.7) (3.8)

(3.8)

.

.

(1)

(1)