|

|

Суперскалярные архитектурыОдин конвейер — хорошо, а два — еще лучше. Одна из возможных схем процессора с двумя конвейерами показана на рис. 2.4. В ее основе лежит конвейер, изображенный на рис. 2.3. Здесь общий блок выборки команд вызывает из памяти сразу по две команды и помещает каждую из них в один из конвейеров. Каждый конвейер содержит АЛ У для параллельных операций. Чтобы выполняться параллельно, две команды не должны конфликтовать из-за ресурсов (например, регистров), и ни одна из них не должна зависеть от результата выполнения другой. Как и в случае с одним конвейером, либо компилятор должен гарантировать отсутствие нештатных ситуаций (когда, например, аппаратура не обеспечивает проверку команд на несовместимость и при обработке таких команд выдает некорректный результат), либо за счет дополнительной аппаратуры, конфликты должны выявляться и устраняться непосредственно в ходе выполнения команд. С1 С2 ' С4 С5 Рис. 2.4. Сдвоенный пятиступенчатый конвейер с общим блоком выборки команд Сначала конвейеры (как сдвоенные, так и обычные) использовались только в RISC-компьютерах. У процессора 386 и его предшественников их не было. Конвейеры в процессорах компании Intel появились, только начиная с модели 4861. Процессор 486 имел один пятиступенчатый конвейер, a Pentium — два та- ких конвейера. Похожая схема изображена на рис. 2.4, но разделение функций между второй и третьей ступенями (они назывались декодер 1 и декодер 2) было немного другим. Главный конвейер(u-конвейер) мог выполнять произвольные команды. Второй конвейер(v-конвейер) мог выполнять только простые команды с целыми числами, а также одну простую команду с плавающей точкой(FXCH). Имеются сложные правила определения, является ли пара команд совместимой в отношении возможности параллельного выполнения. Если команды, входящие в пару, были сложными или несовместимыми, выполнялась только одна из них (в u-конвейере). Оставшаяся вторая команда составляла затем пару со следующей командой. Команды всегда выполнялись по порядку. Таким образом, процессор Pentium содержал особые компиляторы, которые объединяли совместимые команды в пары и могли порождать программы, выполняющиеся быстрее, чем в предыдущих версиях. Измерения показали, что программы, в которых применяются операции с целыми числами, при той же тактовой частоте на Pentium выполняются почти в два раза быстрее, чем на 486 [168]. Вне всяких сомнений, преимущество в скорости было достигнуто благодаря второму конвейеру. Переход к четырем конвейерам возможен, но требует громоздкого аппаратного обеспечения (отметим, что компьютерщики, в отличие от фольклористов, не верят в счастливое число три). Вместо этого используется другой подход. Основная идея — один конвейер с большим количеством функциональных блоков, как показано на рис. 2.5. Pentium И, к примеру, имеет сходную структуру (подробно мы рассмотрим ее в главе 4). В 1987 году для обозначения этого подхода был введен термин суперскалярная архитектура [5]. Однако подобная идея нашла воплощение еще тридцатью годами ранее в компьютере CDC 6600. Этот компьютер вызывал команду из памяти каждые 100 не и помещал ее в один из 10 функциональных блоков для параллельного выполнения. Пока команды выполнялись, центральный процессор вызывал следующую команду. С4 Рис. 2.5. Суперскалярный процессор с пятью функциональными блоками Со временем значение понятия «суперскалярный» несколько изменилось. Теперь суперскалярными называют процессоры, способные запускать несколько команд (зачастую от четырех до шести) за один тактовый цикл. Естественно, чтобы передавать все эти команды, в суперскалярном процессоре должно быть несколько функциональных блоков. Поскольку в процессорах этого типа, как правило, предусматривается один конвейер, его устройство обычно соответствует рис. 2.5. В свете такой терминологической динамики на сегодняшний день можно утверждать, что компьютер 6600 не был суперскалярным с технической точки зрения — ведь за один тактовый цикл в нем запускалось не больше одной команды. Однако при этом был достигнут аналогичный результат — команды запускались быстрее, чем выполнялись. На самом деле разница в производительности между

Предсказание переходов. При выполнении условной команды конвейер приостанавливается так как неизвестно по какой ветви будет продолжаться вычисление. Предсказание переходов позволяет произвести выборку и декодирование команды по одной из ветвей недожидаясь вычисления условия. Способ может быть статическим при этом жестко закладывается какой из результатов более вероятен. Либо динамическим, при нем ведется статистика переходов и вычисление ведется по ветви, результат которой чаще встречается в статистике. Выполнение по предложению. Полностью основывается на предсказании переходов, но команда не только считывается из памяти и декодируется, но и начинается ее выполнение. Шины расширения. Предназначен для подключения различных контроллеров периферийных устройств с целью увеличения функциональных возможностей компьютера. Шины расширения позволяют подключаемым устройствам использовать системные ресурсы. Системные ресурсы. 1. Пространство RAM. 2. Пространство адресов ввода-вывода(порты ввода-вывода). 3. Линии запроса на прерывание. 4. Линии запроса прямого доступа к памяти.

Конфигурирование. -выделение системных ресурсов для контроллера внешних устройств. Для того, чтобы обратиться к устройству оно должно предварительно быть сконфигурировано. Конструктивно шина расширения оформляется в виде щелевых разъемов, называемых слотами. Пропускная способность - количество данных, которое можно передать по шине за один раз. Расчитывается умножением разрядности шины на частоту работы.

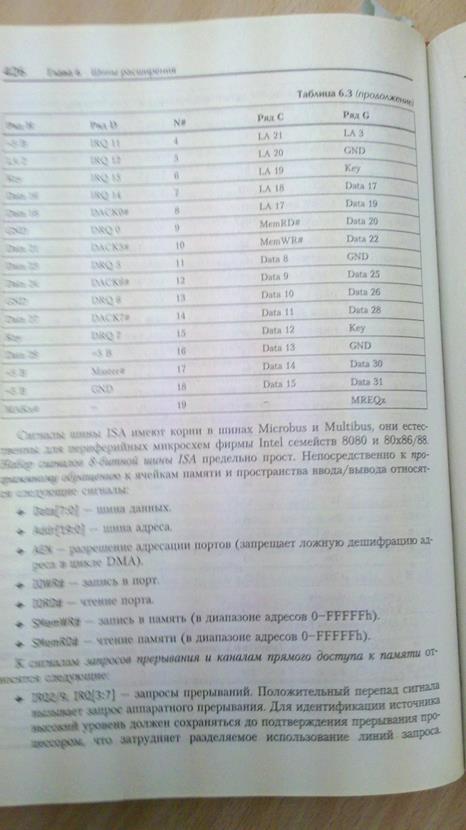

Шина ISA ISA Bus(Industry Standard Architecture)- шина расширения, применявшаяся с первых моделей РС и ставшая промышленным стандартом. В компьютере ХТ использовалась шина с разрядностью данных 8 бит и адреса- 20 бит. В компьютерах АТ ее расширили до 16 бит данных и 24 бит адреса. В таком виде она существует и поныне. Конструктивно шина выполнена в виде двух щелевых разьемов с шагом вывода 2,54 мм(0,1 дюйма)(см.рис4.3). подмножество ISA-8 использует только 62- контактный слот (ряды А,В), в ISA-16 применяется дополнительный 36-контактный слот (ряды С,Д). Шина обеспечивает возможность отображения 8- ил 16-битных регистров на пространство ввода/вывода и памяти. Диапазон адресов памяти ограничен областью UMA (выше А0000h). Для шины ISA-16 опциями BIOS Setup может быть разрешено пространство между 15-м и 16-м мегабайтами памяти(при этом компьютер не сможет использовать более 15 Мбайт ОЗУ). Диапазон адресов ввода/вывода сверху ограничен количеством используемых для дешифрации бит адреса, нижняя граница ограничена областью адресов 0-FFh, зарезервированных под устройства системной платы. В РС была принята 10-битная адресация ввода/вывода, при которой линии адреса а[15.10] устройствами игнорировалась. Таким образом, диапазон адресов устройств шины ISA ограничивается областью 100h-3FFh, то есть всего 758 адресов 8-битных регистров. На некоторые из адресов претендуют системные устройства(см. табл. А.1). впоследствии стали применять 12-ьитную адресацию(диапазон 100h-FFFh). При ее использовании необходимо учитывать возможность присутствия на шине старых 10-битных адаптеров, которые «отзовутся» на адрес с подходящими ему битами А[9:0] во всей допустимой области 12-битного адреса четыре раза(у каждого 10-битного адреса будет еще по три 12-битных псевдонима). D18 D1 B31 B1 рисунок 4.3. слот ISA

C18 C1 A31 A1 Шина ISA-8 может предоставить до 6 линий запросов прерываний, ISA-16-11. Часть их могут «отобрать» устройства системной платы или шина PCI. Шина позволяет использовать до трех 8-битных каналов DMA. На 16-битной шине доступны еще три 16-битных канала. Сигналы 16-битных каналов могут использоваться для прямого управления шиной устройством Bus-Master. При этом канал DMA применяется для арбитража шины, а адаптер Bus-Master формирует все адресные и управляющие сигналы шины, не забывая передать управление шиной процессору не позднее, чем через 15 мкс (чтобы не нарушить регенерацию памяти).

Керниган, Ричи дремучие 70-е года. Шина ISA. Шина является асинхронной. Шина ISA -8 может предоставить до 6 линий запроса прерываний. Шина ISA-16 до 11. Для нормального функционирования шины ее ресурсы должны быть бесконфликтно распределены, т.е каждое устройство должно управлять шиной данных только при чтении по своим адресам и по используемому канала DMA. Области адресов для чтения не должны пересекаться. Так же необходимо назначить линии IRQ, неиспользуемые линии прерываний управляться устройством не могут.

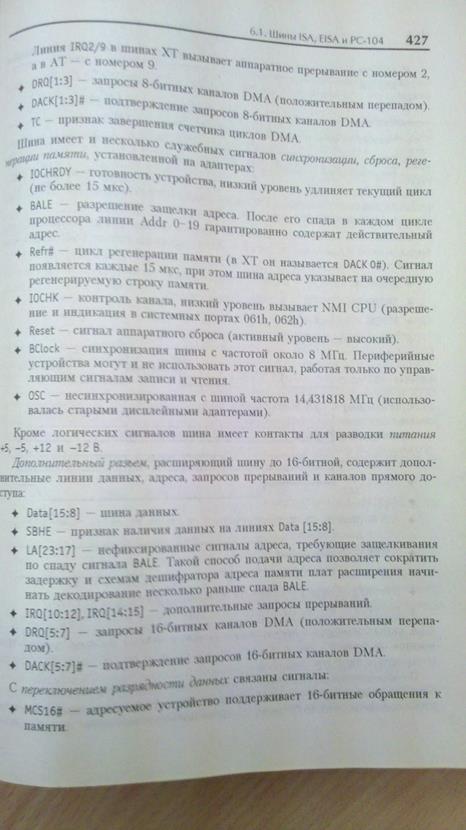

Набор сигналов ISA8. Программное обращение к ячейкам памяти и простанству ввода-вывода обеспечивают следующие сигналы: · Data [7:0] - шина данных · Addr [19:0] - шина адреса · AEN - разрешение адресации портов. · IOWR# - запись в порт · IORD# - чтение из порта · SMemWR# - запись в память · SMemWR# - чтение из памяти

Сигналы запроса прерывания и прямого доступа. IRQ2/9;IRQ [7:3] DRQ [1:3] - запросы 8-битных каналов DMA DACK [1:3] - подтверждение запросов 8-битного канала DMA TC - признак завершения цикла DMA.

Сигналы синхронизации, сброса и регенерации памяти. IOCHRDY - готовность устройства. Низкий уровень удлиняет текущий цикл. BALE - разрешение защелки адреса. После его спада в каждом ццикле процессора лини ADR0-19 гарантированно содержат действительный адрес.

Reset - сигнал аппаратного доступа BClock - синхронизация шины с частотой около 8Мгц OSC - частота 14, 43, 18, 18 Мгц. Кроме логических сигналов шина имеет контакты для заводки питания. +5В, -5В. +12, -12В Шина PCI. (Шина периферийных устройств) Спецификация PCI Описание 1.0 1992г Оригинальная 32/64 разрядная шина Intel. 2.0 1993г Определены соединители и платы расширения 2.1 1995г Появление универсальных карт работа в слотах 5В на частоте 33Мгц и в слотах 3В, частота 66Мгц. 2.2 1999г Создан универсальный разъем, внедрено управление режимом питания 2.3 Карта расширения имеют универсальный разъем, но не способны работать в слотах 5 ранних версий mini-PCI 1999г , основан на PCI 2.2 для мобильных ПК. 3.0 продолжение перехода в слот 3.3В. 64.1 удвоение линий данных и пропускной способности. Слот PCI 64- удлиненный слот PCI. Питание 5В. 64.2 принято напряжение 3.3В. 66 представляет собой протокол PCI 64 предназначенный для частоты 66 Мгц. Питание слотов 3.3 В. Карты универсальные либо форм фактор 3.3 В. 64/66 представляет комбинацию 64 и 66. Позволяет учетверить скорость передачи данных по сравнению с базовым стандартом PCI использует 64-разрядные 3.3В слоты, совместимые только с универсальными и 3.3В 32-разрядными картами расширения. Х.1 представляет расширение 64. Для всех вариантов шины существуют слудующие ограничения по количеству подключаемых к каждой шине устройства: 66 Мгц-4.100 Мгц -3,133 Мгц-1(или 2). Введен механизм раздельных транзакций для улучшения производительности нескольких одновременно работающих устройств. Карты выполняются в 64-разрядном формате 3.3В, имеют ограниченную обратную совместимость со слотами 64/66 или в универсальном формате и способны работать с 2.2/2.3. Х.2 2002 год. Введены частоты 266 и 533 Мгц коррекция ошибок четности при передачи данных ЕСС. Пространство конфигурации расширено. Изменено напряжение 1.5 В, сохранена совместимость разъемов с картами 3.3В.

Шина PCI является локальной, т.е ее контроллер подключается к системной шине. Шина синхронная. Для подачи данных и адреса используется мультиплексированные линии(AD31 AD0). Для передачи команд устройств используется мультиплексированные линии C/BE3-C/BE0. Команды передаются по этим линиям в фазе адреса, в фазе данных по ним передаются сигналы выбора байт на линиях данных. Транзакции шины PCI. На шине PCI одно устройство всегда являются ведущим, остальные ведомыми. В начале обмена ведущее устройство выбирается из ведомых устройств, при помощи сигнала DEVSEL.

Шина АГП. Это 32-битная специализированная шина работающая на 66 Мгц. Шина основана на шине PCI, поэтому использует все принципы работы шины PCI(сигналы шины PCI).

Ускоренность порта обуславливается: 1. Конверизация обращения к памяти. На шине PCI при обработке запроса шина простаивает , конвеер AGP позволяет посылать новый запрос во время обработки текущего. Конвеер может отработать очередь длинной до 256 запросов. 2. Демультиплексирование шины данных и шины адреса. Разделение линий привело к появлению отдельной шины данных DB31-DB0и 8 линий CBA7-CBA0. В котором в последовательном виде передаются адресы команд . 3. Сдвоенная передача данных. По фронту и спаду синхронизирующей последовательности. Кроме того существуют различные спецификации шины в которой множитель обозначает количество 4 байтных слов. Передаваемых за 1 такт. Система прерываний. ПРЕРЫВАНИЯ - это остановка текущей программы по запросу, сохранение «контекста» и переход на процедуру обработчик прерывания с последующим возвратом в основную программу. Прерывания бывают 1) программные - вызываются программой int с указанием номера прерывания. 2) исключения или ловушки - прерывания генерируются в результате внутренней ошибки процессора. 3) аппаратные прерывания - это прерывания, генерируемые одним, из каких либо из углов ПК. 3.1) маскируемые- поступают на вход процессора, генерируется каким либо устройством при возникновения у него события требующего обработки. 3.2) не маскируемые- возникают в результате критических ошибок аппаратуры поступают на входы SMI или NMI процессора. Маскируемые аппаратные прерывания Запросы поступают процессору на вход int r, прерывания называются маскируемые так как можно задать маску то есть правило разрешающее либо запрещающее реакцию системы на прерывания . Для управления маскируемыми аппаратными прерываниями существует флаг разрешения прерываний . Флаг IF глобальное разрешение прерываний. Для управления им служит 2 команды. CLI(IF=>0) запрещает прерывания. STI(IF=>1) разрешает прерывания. Вектор прерываний- это ссылка содержащая адрес программы обработчика данного прерывания. Таблица векторов прерываний- это область ОП выделенная в младших адресах для хранения векторов прерывания. Каждый вектор состоит из 4 байт младшее слова имеет, относительный адрес обработчика, старшее слово базу. Таблица располагается в диапазоне 0000-03FFh. Объем таблицы 1 килобайт она содержит 256 векторов. Каждый PHP содержит 3 регистра: IRR-регистр предназначен для фиксирования запросов поступающих на входы пкп если на вход поступает запрос то соответствующий разряд регистра устанавливается в 1. IMR -предназначен для хранения маски, единица в разряде регистра запрещает реакцию на данное прерывание. ISR-служит для хранения номера обрабатываемого прерывания и построения очереди. Программирование контролера осуществляется при помощи приказов инициализации(ISW) и обработчик приказов(OSW). Используется 4 приказа инициализации. ISW1- передается в пкп ведущий по адресу 020h, ведомый по 0А0h. Остальные ISW2,ISW3,ISW4 передаются в ведущий ПКП по адресу 021h, ведомый 0А1h. Реакция системы прерываний на поступление запросов. Пусть запрос поступит на линию IRQ0. В регистре ПКП IRR фиксируется запрос установкой нулевого бита в единицу. Проверяется маска если нулевой разряд регистра IMR равен 1 то регистр считается замаскированным, дальнейшая обработка не производится, значение регистра IMR сбрасывается. Если разряд = 0 и приоритет у входа достаточно высокий с выхода ПКП IN формируется запрос процессору на вход INT R. Процессор получив запрос от PHP проверяет флаг глобального расширений прерываний. Если прерывания запрещены IF=0, обработка будет отложена до разрешения прерываний. IF=1 то процессор завершает обработку текущей команды сохраняя контекст формирует цикл магистрали. Получив признак этого цикла, системный контроллер передает сигнал на вход пкп. INT A. Шифратор приоритетов пкп уменьшает приоритет обрабатываемого входа по шине данных пкп передает процессору вход команды KALL и номер вектора прерывания. Процессор преобразует полученный номер в адрес вектора таблицы векторов, считывает адрес данного вектора(4 байта). Младшее слово будет являться смещением, и будет помещаться в регистр IP. Старше слово будет являться базой и будет помещено в регистр CS. Следующая команда будет выполнена по загруженному адресу, то есть начнется выполнение обработчика прерывания. 1. Прерывание может быть сгенерировано в любой момент времени, поэтому необходимо в первую очередь сохранить контекст, то есть значение регистра. Команды PUSHA. Завершение обработчика должно производиться восстановлением значений регистров командой POPA. 2. Для предотвращения возникновения повторных прерываний во время обработки текущего необходимо запретить прерывания сбросив флаг глобального разрешения прерываний. 3. Последними командами обработчика должны быть команды разрешающие прерывания и команда выхода из под программы, при генерировании прерывания необходимо обращать внимание на регистры CS, IP, FLAGS. Для восстановления регистров из стека при выходе из под программы используется команда IRET. Таким образом общий вид можно представить

Не нашли, что искали? Воспользуйтесь поиском по сайту: ©2015 - 2026 stydopedia.ru Все материалы защищены законодательством РФ.

|