|

|

Шина управления SMI интерфейса МПВ спецификации IEEE 802.3u сетевой технологии Ethernet от 1995 г. появился интерфейс МП (Media Independent Interface — интерфейс, независимый от среды передачи), позволяющий отделять специфические устройства физического уровня (PHY) от вышестоящих уровней. Кроме интерфейса передачи «полезных» данных сети в МП входит последовательный интерфейс SMI (Serial Management Interface), обеспечивающий доступ к внутренним регистрам PHY. Эти регистры позволяют отслеживать состояние PHY и управлять им; в частности, и управлять согласованием режимов сетевых портов. В спецификации описаны регистры, обязательные для устройств, а также отведено место для специфических регистров, используемых по воле разработчика. Интерфейс SMI представляет собой последовательную синхронную трехпроводную шину (сигналы MDC, МОЮ и шина GND), обеспечивающую доступ по записи и чтению к 16-разрядным регистрам устройств. Протокол шины обеспечивает 5-битную адресацию подключаемых устройств, что позволяет непосредственно объединять до 32 устройств на одной шине. Каждое устройство может иметь до 32 регистров. Шина является хост-центрической — ею управляет один контроллер, инициирующий транзакции, а все подключаемые устройства являются ведомыми. Контроллер генерирует импульсы синхронизации по однонаправленной линии MDC, а по двунаправленной линии МОЮ формирует биты команд и данных (при записи) и принимает данные чтения. Устройство, опознавшее свой адрес, должно выполнить адресуемую ему команду. Уровни сигналов — обычные для логики ТТЛ и КМОП; для линии МОЮ обычно используются формирователи с открытым коллектором (стоком) и резисторы, «подтягивающие» пассивную линию к уровню питания (+5 или +3,3 В). Частота импульсов MDC, не обязательно постоянная, не должна превышать 2,5 МГц, что позволяет реализовать функции контроллера чисто программно. Временные диаграммы сигналов для транзакций чтения и записи приведены на рис. 11.4. Отметим, что устройство должно фиксировать биты по положительному перепаду MDC, а контроллер фиксирует биты по отрицательному перепаду. Адреса и данные передаются начиная со старших бит.

Рис. 11.4.Транзакции на шине SMI: a — запись, б — чтение 444__________ Глава 11. Вспомогательные последовательные интерфейсы и шины В общем случае каждой транзакции должна предшествовать преамбула Рге — не менее 32 тактов нахождения МОЮ на высоком уровне. Собственно транзакция начинается с условия Start — вывода контроллером битовой последовательности «01», за которым следует двухбитная команда Cmd: «10» — чтение или «01» — запись. Далее контроллер передает 5-битный адрес устройства (PhyAd), за которым следует 5-битный номер регистра (RegAd). После этого следует двухбитный «пируэт» (turnaround) ТА для перехода к передаче данных. При операции записи «пируэт» сводится к передаче контроллером последовательности «10», а затем он передает 16 бит данных (WData) для записи в регистр. При чтении с начала «пируэта» контроллер отпускает линию МОЮ, а на время второго бита отозвавшееся адресованное устройство устанавливает на этой линии нуль, что используется для определения факта ответа. В следующие 16 тактов устройство передает считанные данные (RData) контроллеру. Преамбула нужна только для приведения интерфейсной части устройств в исходное состояние (после подачи питания); если питание устройством не терялось, то последующие транзакции могут выполняться и без преамбулы. Имеется также нюанс в «пируэте»: для некоторых устройств второй его бит оказывается лишним — он сбивает синхронизацию данных на 1 такт. Интерфейс SPI Интерфейс SPI (Serial Peripheral Interface), он же Microwire, — трехпроводный синхронный с раздельными линиями входных и выходных данных — применяется для связи микроконтроллеров с периферийными микросхемами и микросхемами памяти. С его помощью программируются многие микросхемы программируемой логики (например, FPGA фирмы Altera), применяемые в различных узлах ПК и периферии. По сравнению с 12С интерфейс SPI обеспечивает более высокую скорость передачи данных. Частота синхронизации может достигать 5 МГц (зависит от подключаемых устройств); при этом за каждый такт синхронизации одновременно может и передаваться, и приниматься очередной бит данных. В основном варианте использования предполагается, что интерфейс соединяет одно ведущее устройство с одним или несколькими ведомыми устройствами. Интерфейс может применяться и для обмена между несколькими микроконтроллерами, допуская наличие на шине нескольких ведущих устройств, но протокол предоставления доступа не стандартизован. Ниже рассматривается работа интерфейса с одним ведущим устройством. В интерфейсе используются 3 обязательных сигнала: ♦ SCK (Serial Clock) — синхросигнал, которым ведущее устройство стробирует каждый бит данных; ♦ MOSI (Master Output Slave Input) — выходные данные ведущего устройства и входные данные ведомого устройства; ♦ MISO (Master Input Slave Output) — входные данные ведущего устройства и выходные данные ведомого устройства. 11.3. Интерфейс SPI

Возможен и иной способ общения ведущего устройства с несколькими ведомыми устройствами с чисто шинной топологией. Здесь сигнал SS# для выбора устройств не используется, но ведомые устройства все время «слушают» шину, ожидая специальной адресной посылки в начале транзакции. Опознав свой адрес, устройство отрабатывает дальнейшие протокольные посылки, и теперь ему разрешается выводить данные на линию MISO до конца текущей транзакции. Однако этот вариант требует довольно сложной логики поведения ведомого устройства.

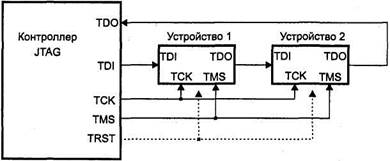

Рис. 11.5. Форматы передач по интерфейсу SPI Данные передаются старшим битом вперед. Устройства различных производителей могут использовать разные режимы обмена (SPI Mode 0... SPI Mode 3), различающиеся фазой и полярностью синхросигналов. Рис. 11.5 иллюстрирует передачу и прием байта в различных режимах. Заметим, что в любом режиме входные и выходные данные стробируются по разным перепадам синхроимпульсов. Кроме того, есть варианты в использовании сигнала SS#. В первом варианте (он и представлен на рисунке) для ведомого устройства признаком начала транзакции является спад сигнала SS#, а завершения — его подъем. Во втором варианте начало транзакции определяется по первому фронту (спаду) SCK, а сигнал SS# может иметь низкий уровень постоянно. Второй вариант иногда предпочитают для простейшего двухточечного интерфейса с единственным ведущим устройством и единствен- 446__________ Глава 11. Вспомогательные последовательные интерфейсы и шины ным ведомым устройством, когда нет опасения потери синхронизации. Микроконтроллеры с аппаратным портом SPI, как правило, имеют возможность программного выбора режима. Форматы транзакций зависят от устройств, но общая идея такова: ведущее устройство по линии MOSI посылает код операции и адресную информацию для устройства; затем следуют данные. В операции записи они передаются ведущим устройством по той же линии, в операции чтения устройство их посылает по линии MISO. На время всей транзакции ведущее устройство сохраняет активное состояние линии SS#, число требуемых синхроимпульсов зависит от формата команды. Интерфейс JTAG Интерфейс JTAG (Joint Test Action Group) предназначен для тестирования сложных логических схем, установленных в целевое устройство. Этот интерфейс описан в стандарте IEEE 1149.1 Boundary Scan Architecture и является последовательным синхронным, но в связи со спецификой назначения значительно отличается от вышеописанных интерфейсов, ориентированных на передачу данных. Интерфейсом JTAG управляет одно устройство-контроллер (чаще всего это ПК с соответствующим интерфейсным адаптером), к которому может быть подключено несколько тестируемых устройств. Ниже перечислены сигналы интерфейса JTAG. ♦ ТСК (Test Clock) — сигнал синхронизации последовательных данных; генерируется контроллером. Частота синхронизации может достигать 16 МГц. ♦ IMS (Test Mode Select) — сигнал выбора тестового режима. Генерируется контроллером. ♦ TDI (Test Data Input) — входные данные, принимаемые устройством в последовательном двоичном коде (младшим битом вперед). ♦ ТОО (Test Data Output) — выходные данные, передаваемые устройством в последовательном двоичном коде. ♦ TRST (Test Logic Reset) — необязательный сигнал сброса логики интерфейсного порта, генерируемый контроллером. Эти сигналы (все однонаправленные), имеющие обычные логические уровни, образуют тестовый порт ТАР (Test Access Port), через который тестируемое устройство подключается к тестирующему оборудованию (контроллеру). В задачу тестирующего оборудования входит формирование тестовых сигналов по программе тестирования, определенной разработчиком тестируемого устройства, и сравнение полученных результатов с эталонами. Один и тот же контроллер и порт могут использоваться для тестирования любого числа устройств, поддерживающих JTAG. Для этого устройства своими портами ТАР соединяются в цепочку (рис. 11.6). Стандартизованный логический формат позволяет контроллеру независимо общаться с каждым из устройств цепочки (для этого, конечно, они должны иметь исправные ячейки JTAG). 11.4. Интерфейс JTAG

Рис. 11.6. Цепочка устройств с интерфейсом JTAG Идею тестирования любой цифровой схемы иллюстрирует рис. 11.7, на котором показана условная цифровая система, имеющая входные, выходные (возможно, с третьим состоянием) и двунаправленные сигналы. Ячейки тестирования B/S врезаются между реальными внешними выводами устройства и собственно логическим устройством, то есть располагаются на логической границе (boundary) устройства. ТАР-контроллер способен сканировать ячейки — управлять ими и считывать с них информацию. Отсюда и пошло название Boundary Scan, которое можно перевести как «периферийное сканирование». При включенном тестовом режиме ТАР-контроллер может логически отсоединить сигналы от внешних выводов, задавать входные воздействия и считывать результаты — собственно, это все, что необходимо для тестирования последовательностных схем (автоматов с памятью). Прелесть JTAG заключается в том, что независимо от сложности устройства оно тестируется с помощью всего лишь четырех сигналов — все сложности прячутся в достаточно простые ячейки, «окутывающие» его сигнальные выводы. Тестовая логика, встраиваемая в устройство, поддерживающее JTAG, состоит из следующих элементов: ♦ тестовый порт ТАР (четыре интерфейсных сигнала); ♦ ТАР-контроллер, управляющий тестовыми регистрами; ♦ регистр инструкций IR (Instruction Register), который принимает последова ♦ регистры тестовых данных, из которых любое устройство должно иметь три Регистры инструкций и данных представляют собой независимые сдвиговые регистры, соединенные параллельно. На их входы (старшие биты) приходит сигнал TDI, с выходов (младшие биты) снимается сигнал ТОО. По каждому положительному перепаду данные продвигаются на один бит. Регистр В Р R имеет длину в один бит. Он используется как кратчайший обходной путь для последовательных данных, когда остальные регистры не участвуют в обмене. Глава 11. Вспомогательные последовательные интерфейсы и шины

Рис.11.7. Включение ячеек сканирования Регистр BSR представляет собой длинный сдвигающий регистр, каждым битом которого являются пограничные ячейки, установленные на всех входных и выходных сигналах процессора. Для двунаправленных сигналов (или их групп), кроме собственно информационных ячеек регистра, соответствующих внешним сигналам, имеются и управляющие ячейки, задающие режим работы информационных ячеек. К примеру, у процессоров Р6 длина BSR составляет 159 бит. Регистр DID длиной 32 бита содержит идентификатор производителя, код устройства и номер версии, по которым ТАР-контроллер может распознать, с каким устройством он имеет дело. Регистр IR служит для хранения исполняемой тестовой инструкции. Его длина зависит от тестируемого устройства. Для всех устройств обязательными являются инструкции BYPASS, IDCODE, SAMPLE и EXTEST. Инструкция BYPASS (все биты кода — единичные) предназначена для подключения однобитного обходного регистра, обеспечивая скорейшее прохождение данных через устройство; при этом оно никак не реагирует на проходящий поток. Вход TDI обычно «подтягивают» резистором к высокому уровню, при этом разрыв цепочки JTAG приведет к подключению обходных регистров во всех устройствах после точки обрыва. Это исключает возможные непредсказуемые действия устройств в случае обрыва. 11.4. Интерфейс JTAG________________________________________________ 449 Инструкция идентификации IDCODE (младшие биты кода — 10) подключает к интерфейсу регистр DID, позволяя считать его содержимое (поступающие входные данные не могут изменить его значение). Инструкция SAMPLE/PRELOAD (младшие биты кода — 01) имеет два назначения. Когда ТАР-контроллер находится в состоянии Capture-DR (см. ниже), эта инструкция позволяет выполнить моментальный «снимок» состояния всех внешних сигналов без воздействия на работу устройства. Значение сигналов фиксируется по положительному перепаду ТСК. В состоянии Update-DR по этой инструкции данные загружаются в выходные ячейки тестового порта (но еще не на выходы устройства), откуда впоследствии они будут выводиться (подаваться на выводы процессора) по инструкции EXTEST. Данные загружаются по спаду сигнала ТСК. Инструкция EXTEST (младшие биты кода — 00) предназначена для проверки внешних цепей (по отношению к тестируемому устройству). При этом на выходные выводы подаются сигналы, предварительно записанные в регистр BSR, а состояние входных сигналов фиксируется в этих регистрах. Двунаправленные сигналы предварительно конфигурируются соответствующими им управляющими битами ячеек BSR. Стандарт 1149.1 предусматривает и инструкцию тестирования внутренней логики устройства INTE5T, но ее поддерживают не все устройства. Контроллер тестового порта (TAP-controller) представляет собой синхронный конечный автомат, изменяющий состояние по фронту сигнала ТСК и по включению питания. Сменой состояний управляет сигнал TMS (Test Mode State), воспринимаемый по положительному перепаду ТСК. Граф состояний и переходов управляющего автомата представлен на рис. 11.8. Около стрелок переходов указаны значения сигнала TMS во время фронта ТСК. В исходное состояние Test-Logic-Reset контроллер автоматически переходит по включении питания и из любого другого состояния может быть переведен высоким уровнем TMS, удерживаемым не менее пяти тактов ТСК. Для перевода в состояние Test-Logic-Reset иногда используют и дополнительный сигнал TRST. В этом состоянии тестовая логика запрещена, и устройство работает в нормальном режиме. Состояние Run-Test/Idle является промежуточным между выполнением тестовых операций. В этом состоянии регистры не изменяют своего значения. В состоянии Capture-DR во время выполнения инструкций EXTEST и SAMPLE/ PRELOAD сканирующий регистр фиксирует только данные на входных линиях. В состоянии Shift-DR данные с TDI продвигаются через подключенный сдвиговый регистр на выход ТОО. В состоянии Pause-DR контроллер временно запрещает продвижение данных через сдвиговый регистр. В состоянии Update-DR по спаду ТСК сигналы из сдвигового регистра фиксируются на' выходах тестовых ячеек. В состоянии Capture-IR контроллер загружает в сдвиговый регистр инструкций код «безобидной» инструкции SAMPLE. 450 Глава 11. Вспомогательные последовательные интерфейсы и шины

Рис.11.8. Граф состояний и переходов контроллера ТАР В состоянии Shift-IR в цепь между TDI и ТОО включается сдвиговый регистр инструкций, но еще исполняется предыдущая инструкция. В состоянии Pause-IR контроллер временно запрещает продвижение данных через сдвиговый регистр инструкций. В состоянии Update-IR по спаду ТСК фиксируется новая исполняемая инструкция, и в цепь TDI-TDO включается соответствующий ей регистр. Кроме этих основных состояний контроллера, определяющих действия тестового оборудования, имеются и временные промежуточные состояния, необходимые для реализации переходов автомата. К ним относятся Select-DR-Scan, Exti1-DR, Exit2-DR, Select-DR-Scan, Exit1-IR и Exit2-IR. Для интерфейса JTAG существует специальный язык описания устройств BSDL (Boundary Scan Description Language). Состав и порядок следования информаци- 11.5. Программно-управляемая реализация последовательных интерфейсов 451 онных и управляющих ячеек в сдвиговом регистре данных специфичен для каждого устройства (для чего и существует идентификационный регистр) и сообщается его разработчиками. Интерфейс JTAG используется не только для тестирования, но и для программирования различных устройств, в том числе и энергонезависимой памяти микроконтроллеров. Контакты для сигналов JTAG имеются на шине PCI, однако в их использовании единообразия не наблюдается (либо остаются неподключенными, либо соединяются для организации цепочки). Интерфейс JTAG имеется в современных процессорах; здесь он позволяет не только тестировать сам процессор (это не представляет особого прикладного интереса), но и организовать зондовый режим отладки (probe mode, см. [6, 7]). Зондовый режим является мощным средством отладки системного программного обеспечения; обычный процессор, связанный с тестовым контроллером интерфейсом JTAG, превращается во внутрисхемный эмулятор — мечту разработчика системного ПО.

Не нашли, что искали? Воспользуйтесь поиском по сайту: ©2015 - 2026 stydopedia.ru Все материалы защищены законодательством РФ.

|

Кроме того, может использоваться сигнал выбора ведомого устройства SS# (Slave Select, или CS# — Chip Select): ведомое устройство должно реагировать на сигналы интерфейса и генерировать выходные данные на линии MISO только при низком уровне этого сигнала; при высоком уровне выход MISO должен переводиться в высокоимпедансное состояние. С помощью сигналов SS#, раздельно формируемых ведущим устройством для каждого из ведомых устройств, ведущее устройство может выбирать партнером в транзакции одно из ведомых. При этом получается гибридная топология соединений: по сигналам SCK, MOSI и MISO — топология шинная, по SS# — звездообразная (центр — ведущее устройство).

Кроме того, может использоваться сигнал выбора ведомого устройства SS# (Slave Select, или CS# — Chip Select): ведомое устройство должно реагировать на сигналы интерфейса и генерировать выходные данные на линии MISO только при низком уровне этого сигнала; при высоком уровне выход MISO должен переводиться в высокоимпедансное состояние. С помощью сигналов SS#, раздельно формируемых ведущим устройством для каждого из ведомых устройств, ведущее устройство может выбирать партнером в транзакции одно из ведомых. При этом получается гибридная топология соединений: по сигналам SCK, MOSI и MISO — топология шинная, по SS# — звездообразная (центр — ведущее устройство).