|

|

Модули динамической памятиДинамическая память чаще всего применяется в виде модулей с разрядностью 1, 2,4 или 8 байт, которые могут устанавливаться пользователем без каких-либо приспособлений. Модули стандартизованы, поэтому обеспечивается взаимная совместимость. ♦ SIPPh SIMM-30 — самые первые модули с однобайтной организацией, применялись вплоть до 486-х процессоров. ♦ SIMM-72-pin — 4-байтные модули, применявшиеся на системных платах для 486 и Pentium. 252________________________________ Глава 7. Интерфейсы электронной памяти ♦ DIMM-168 — 8-байтные модули для Pentium и выше. Существует два поколения, существенно различных по интерфейсу. Модули DIMM 168-pin Buffered (1-го поколения), как и слоты для них, встречаются редко и с широко распространенными модулями DIMM 2-го поколения несовместимы даже механически (по ключам). Наиболее популярно второе поколение с микросхемами SDRAM.Различают модификации в зависимости от наличия буферов или регистров на управляющих сигналах:' Unbuffered, Buffered и Registered. ♦ DIMM-184 — 8-байтные модули DDR SDRAM для системных плат 6-7 поколений процессоров. ♦ RIMM — 2-байтные модули RDRAM для системных плат 6-7 поколений процессоров. ♦ SO DIMM (72 и 144-pin) и 50 RIMM — малогабаритные варианты модулей (для блокнотных ПК). ♦ AIMM (AGP Inline Memory Module), они же GPA Card (Graphics Performance Accelerator) — 66-контактные 32- или 16-битные модули SDRAM, предназначенные для расширения памяти графических адаптеров, встроенных в системную плату. Не пересчитывая контакты, отличить «короткие» SIMM от «длинных» и DIMM-модулей легко по их размеру: длина модуля SIMM-30 pin примерно 89 мм, SIMM-72 — 108 мм. Модули DIMM-168 и DIMM-184 имеют одинаковую длину около 134 мм (5,25"), но у 168-контактных модулей два ключа, а у 184-контактных — один (за счет чего больше контактов); кроме того, у DIMM-184 по две прорези по бокам, а не по одной. Модули RIMM имеют ту же длину, но легко отличимы по меньшему числу контактов — середина краевого разъема свободна от ламелей. У модулей RIMM микросхемы памяти закрыты пластиной радиатора. Кроме того, их левый ключ гораздо ближе к центру, чем у DIMM. Модули памяти применяются и в принтерах (лазерных) — DIMM-168, 100-Pin DIMM, AIMM, SO DIMM-144, но иногда для них требуются и специальные модули (по конструктиву или параметрам). Современные модули памяти имеют шину данных разрядностью 1,4 или 8 байт. Кроме основных информационных бит, модули могут иметь дополнительные контрольные биты с различной организацией. ♦ Модули без контрольных бит (поп Parity) имеют разрядность 8,32 или 64 бита и допускают независимое побайтное обращение с помощью отдельных для каждого байта линий CAS#. ♦ Модули с контролем паритета (Parity) имеют разрядность 9, 36 или 72 бита ♦ Модули с генератором паритета (Fake Parity, Parity Generator, Logical Parity) так же допускают независимое побайтное обращение, логические генераторы паритета по чтению приписаны к соответствующим байтам. Действительного контроля памяти они не обеспечивают. 7.1. Динамическая память ♦ Модули с контролем по схеме ЕСС имеют разрядность 36,40,72 или 80 бит. ♦ ECC-Optimized — модули, оптимизированные под режим ЕСС. От обычных модулей ЕСС они отличаются тем, что могут не обеспечивать побайтное обращение к информационным битам. ♦ ECC-on-Simm (EOS) — модули со встроенной схемой исправления ошибок. Каждый байт модуля имеет встроенные средства контроля и исправления ошибок, работающие прозрачно. Для системы модули функционируют как обычные паритетные — в случае обнаружения неисправимой ошибки они генерируют ошибочный бит паритета. Эти модули обеспечивают отказоустойчивость по памяти(Kill Protected Memory) для системных плат, поддерживающих только контроль паритета. По «благородству» поведения (делают больше, чем «говорят»)они являются прямой противоположностью модулям с генератором паритета. Набор сигналов модуля SIMM в основном совпадает с сигналами одиночных микросхем динамической памяти. Основные характеристики распространенных модулей приведены в табл. 7.5, более подробное описание — в следующих разделах. Таблица 7.5.Основные характеристики модулей памяти

1В скобках указана разрядность с учетом битов паритета или ЕСС. Спецификация быстродействия у разных типов памяти отражает различные параметры и выбирается исходя из технических и маркетинговых соображений. Для асинхронной памяти указывают время доступа (в наносекундах). Для памяти SDRAM указывается тактовая частота, на которой она работает с достойным зна- 254________________________________ Глава 7. Интерфейсы электронной памяти чением латентности (на более высокой частоте она, возможно, и будет работать, но с большим значением CL). Обозначения РС66, PC 100 и PC 133 здесь тоже указывают на частоту (отсутствие обозначения соответствует 66 МГц — поначалу иных спецификаций не было), а также на соответствие спецификациям Intel. Для DDR SDRAM числа в спецификации отражают пиковую пропускную способность (Мбайт/с): РС1600 (8 байт, 2 х 100 МГц), РС2100 (8 байт, 2 х 133 МГц). Для RDRAM числа в названии (600, 700 и 800) обозначают округленную частоту (2 х 300, 2 х 356 и 2 х 400 МГц) схода двухбайтных данных с конвейера RDRAM. Таким образом, их пиковая производительность составляет 1200, 1424 и 1600 Мбайт/с. Маркировка модулей SDRAM, согласно спецификациям Intel, имеет вид PCX-abc-defY, где X — частота, МГц; а - CL (Cas Latency, в тактах), b - Trcd (задержка RAS-CAS), с = Тгр (время предзаряда RAS), d - Тас (время доступа), е — ревизия последовательной идентификации (SPD), f — резервный символ, Y — символ архитектурных особенностей (R — признак наличия регистров; отсутствие символа означает отсутствие регистров и буферов). Временные характеристики задаются в десятках не, но Тас может задаваться и в наносекундах. Номер ревизии SDP может содержать как последнюю цифру, так и обе. Так, модуль РС100-322-620 работает на частоте 100 МГц при CL - 3 и Тас = 60 не, SPD ревизии 1.2. Но он может обозначаться и как PC 100-322-60120. Модуль PC100-322-620R имеет те же параметры, но еще снабжен и регистрами. Существуют адаптеры, преобразующие форматы модулей SIMM (SIMMVerter, SIMMSaver). Они позволяют, например, сложить из четырех SIMM-30 один SIMM-72 или из двух односторонних SIMM-72 сложить один двусторонний. Трудно назвать такие конструктивные решения элегантными и надежными (появляется слишком много механических соединений и контактов), но их применение может быть оправданно при дефиците гнезд на плате. Или, например, при наличии четырех 4-мегабайтных модулей SIMM-30 можно сделать 16-мегабайтный SIMM-72. Следует помнить о повышенной нагрузке на шины, вносимой такими «супермодулями» с непомерным количеством микросхем и проводников. Идентификация модулей Для автоматической идентификации наличия и типа установленного модуля применяются различные методы, основанные на считывании конфигурационной информации с модуля (параллельная или последовательная идентификация) или «исследовании» свойств модуля во время начального тестирования по включении питания. Метод параллельной идентификации начал применяться с модулями SIPP и SIMM-30 фирмы IBM. В интерфейс этих модулей были введены два дополнительных вывода, и по заземленным (на модуле) сигналам системная плата могла распознать наличие и объем установленной памяти. В SIMM-72 для идентификации предназначались 4 вывода (для ЕСС-модулей — 5), которые должны были нести информацию об объеме, быстродействии и типе применяемой памяти. Этот метод не выдержал натиска новых типов памяти, поскольку описать их важнейшие 7,1. Динамическая память_____________________________________________ 255 параметры четырьмя битами невозможно. В SO DIMM-72 используют 7 бит, в DIMM-168 первого поколения — 10, что тоже не решает проблем. Новые модули памяти — DIMM-168 второго поколения, SO DIMM-144, DIMM-184 используют последовательную идентификацию (Serial Presence Detection). На модуль устанавливается микросхема специальной энергонезависимой памяти с последовательным доступом по двухпроводному интерфейсу 12С, хранящая исчерпывающую конфигурационную информацию. Формат конфигурационных данных стандартизован JEDEC, из доступных 256 байт под параметры пока определены только первые 32 и еще 32 зарезервированы, 64 байта отданы под информацию производителя (табл. 7.6). Основные параметры описываются в явном виде, например, временные — в наносекундах, количество бит адреса задается числами. Интерфейс 12С позволяет легко объединять его сигналы со всех модулей, что существенно проще, чем коммутация 4-10 линий параллельной идентификации. На разъем модулей DIMM-168 выведены 3 бита адреса SA[0:2], что позволяет разводкой этих выводов адресовать до восьми модулей с объединенными линиями синхронизации и данных. При необходимости расширения следующие восемь модулей потребуют от контроллера (чипсета) еще только одной двунаправленной или выходной линии. Адрес в SO DIMM-144 фиксирован, так что двухпроводный интерфейс позволяет опрашивать только один модуль, а каждый следующий модуль потребует по одной дополнительной линии. Байты 128-255 конфигурационной памяти свободны. Эту область в принципе можно занимать для пометки компьютера (точнее, модуля памяти) с целью привязки программного обеспечения к конкретному экземпляру PC. Однако при неосторожном использовании модулей с микросхемами без защиты от модификации случайная запись в ячейки 0-127 может привести к недоступности модуля памяти. «Оживить» его можно будет только записью корректных данных. Таблица 7.6.Назначение байт последовательной идентификации Байт Назначение

0 Число записанных байт конфигурационной памяти 1 Разрядность адреса микросхемы Serial PD (определяет объем конфигурационной 2 Тип памяти: 00 — резерв, 01 — Std FPM, 02 — EDO, 03 — Pipelined Nibble (BEDO), 3 Количество бит адреса строк в банке 1 (биты 0-3) и банке 2 (биты 4-7) по модулю 16 то биты 4-7 нулевые 4 Количество бит адреса столбцов (аналогично предыдущему) 5 Количество банков (рядов микросхем) 6-7 Разрядность данных с учетом контрольных бит (если менее 255, байт 7 — 0) 8 Уровень напряжения интерфейса: О — 7TL/5B, 01 —LVTTL (не допускает 5 В), 02 — HSTL 1.5,03 — SSTL 3.3,04 — SSTL 2.5

256________________________________ Глава 7. Интерфейсы электронной памяти Таблица 7.6(продолжение) 9 Для DRAM — RAS Access time (в наносекундах). Для SDRAM — минимальное время 10 Для DRAM — CAS Access time (в наносекундах). Для SDRAM — время доступа 11 Схема контроля: 00 — Non-Parity, 01 — Parity, 02 — ЕСС 12 Частота (тип) регенерации: 00 — Normal (распределенный цикл 156 мкс), 01 — Reduced 0.25х (39 мкс), 02 — Reduced 0.5х (78 мкс), 03 — Extended 2x (313мкс), 04 — Extended 4x (625 мкс), 05 — Extended 8x (125 мкс). Бит7 является признаком саморегенерации (биты 6:0 кодируют те же периоды) 13 Разрядность микросхем основной памяти, бит. Бит 7 равен 1, если имеется второй 14 Разрядность микросхем контрольных разрядов, бит (аналогично) 15-30 Детальное описание временных и организационных параметров SDRAM 31 Объемы банков (рядов микросхем): битО —4 Мбайт, бит 1—8 Мбайт, бит7 — 512 Мбайт, единичное значение устанавливается в одном или нескольких (двух) битах 32-35 Время предварительной установки и удержания входных сигналов 36-61 Резерв 62 Ревизия SPD (две BCD-цифры) 63 Контрольная сумма байт 0-62 по модулю 256 64-71 Идентификатор производителя по JEDEC 72 Код страны производителя 73-90 Код изделия (ASCII) 91-92 Код модификации 93-94 Дата изготовления (wwyy — неделя, год) 95-98 Серийный номер 99-127 Специальные данные изготовителя 126 Спецификация частоты (для Intel) DIMM SDRAM. Частота 66 МГц задается кодом 66п, 127 Детализация для SDRAM 100 МГц (для Intel)

Модули SIMM (Single In-Line Memory Module) и SIPP (Single In-Line Pin Package) представляют собой небольшие печатные платы с односторонним краевым разъемом. Контактами модулей SIMM являются позолоченные (или покрытые специальным сплавом) площадки, расположенные на обеих поверхностях вдоль одной из сторон. Слово Single (одиночный) в названии подразумевает, что пары площадок на обеих сторонах эквивалентны (электрически соединяются между собой). У малораспространенных модулей SIPP контакты штырьковые (pin — иголка); эти контакты при необходимости можно припаять к площадкам модулей SIMM (такие контакты 7.1. Динамическая память_____________________________________________ 257 когда-то даже продавались в комплекте с модулями SIMM). Модули SIPP оказались непрактичными — их контакты не выдерживают транспортировки и многократной установки. На модулях смонтированы микросхемы памяти в корпусах SOJ или TSOP, их адресные входы объединены. Количество и тип микросхем определяются требуемой разрядностью и объемом хранимых данных. Архитектура модулей обеспечивает возможность побайтного обращения, что существенно для записи (byte-write); выбор байт производится отдельным входом CAS# для каждого байта. Распространенные модули имеют напряжение питания 5 В, их параметры приведены в табл. 7.7. Таблица 7.7.Организация модулей SIMM

По логической организации различают односторонние и двусторонние модули. «Короткие», или SIMM 30-pin, модули SIMM (старый тип) имеют 30 печатных выводов (рис. 7.11) и однобайтную организацию. Разводка выводов у модулей фирмы IBM (для компьютеров IBM PS/2) отличается от общепринятых стандартных. Различия делают несовместимыми модули с объемом более 1 Мбайт: модули IBM могут быть двусторонними (2 Мбайт), стандартные — только односторонними. Малораспространенные модули SIPP имеют 30 штырьковых выводов и совпадают по разводке со стандартными модулями SIMM 30-pin (SIMM-30). Применение однобайтных модулей особенно в 32-битных системных платах сильно сковывает свободу выбора объема памяти. Назначение выводов SIMM-30 и SIPP приведено в табл. 7.8. Глава 7. Интерфейсы электронной памяти

Рис.711. Модули SIMM-30 Таблица 7.8.Назначение выводов модулей SIPP и SIMM 30-pin

1 STD-стандартный SIMM (SIPP). 2 IBM - SIMM фирмы IBM. «Длинные», или SIMM 72-pin (SIMM-72), модули SIMM имеют 72 печатных вывода (рис. 7.12, табл. 7.9) и 4-байтную организацию с возможностью независимого побайтного обращения по сигналам CASx#. По сигналам выборки строк биты данных делятся на два слова, DQ[0:15] выбираются сигналом RASO# для первого банка и RAS1 # для второго, DQ[ 16:31] выбираются соответственно сигналом RAS2* и RAS3*. В односторонних модулях (1,4,16,64 Мбайт — 1 банк) используется только одна пара сигналов выборки RASO* и RAS2#, в двусторонних (2,8, 32 Мбайт — 2 банка) — две пары сигналов RAS#. Заметим, что использование всеми модулями обеих дар линий RAS# поддерживается не всеми системными платами. Контрольные биты модулей с паритетом по выборке приписываются к соответству1-ющим байтам, в ЕСС-модулях возможны различные варианты. Модули без пари-тета имеют разрядность 32 бит, с паритетом — 36 бит, модули ЕСС — 36 или 40 бит. Модули ЕСС-36 и ЕСС-40 (ECC-optimised) не допускают побайтного обращения и существенно отличаются от 32-битных и паритетных модулей. 7,1. Динамическая память

Рис. 7.12.Модули SIMM-72 Таблица 7.9.Назначение выводов модулей SIMM 72-pin

продолжение^ Глава 7. Интерфейсы электронной памяти Таблица 7.9(продолжение)

Контакт Назначение для модулей х32, Parity/ECC1

2 Могут существенно отличаться по назначению у модулей ЕСС. Сигналы DQ[36:39] имеются только в модулях ЕСС-40. В скобках приведены назначения выводов модулей фирмы IBM. Сигналы модулей SIMM (табл. 7.10) в основном совпадают с сигналами микросхем динамической памяти. Для идентификации модулей предназначены сигналы PD[1:5]. По заземленным (на модуле) сигналам системная плата может распознать быстродействие (тип) и объем установленной памяти. Стандарт JEDEC для SIMM-72 определяет следующее назначение выводов (0 — заземлен, 1 — свободен): ♦ сигналы PD[1: 2] (контакты 67,68) — объем памяти модуля, Мбайт: 00=4,11=8,01=16, 10=32; ♦ сигналы PD[3:4] (контакты 69,70) - время доступа, не: 00=100, 10=80, 01=70,11=60; ♦ сигнал PD5 может являться признаком ЕСС-модуля (заземленный контакт). Таблица 7.10.Сигналы модулей SIMM Сигнал Назначение

DQx Data Bit — биты данных (объединенные входы и выходы) PQx Parity Bit — бит паритета х-го байта PB-ln, Parity Bit Input, Output — вход и выход микросхемы бита паритета (для SIPP PB-Out и SIMM-30). Для хранения паритета в этих модулях всегда используются микросхемы с однобитной организацией, у которых вход и выход разделен. Обычно эти контакты на модуле соединены WE# Write Enable — разрешение записи. При низком уровне сигнала во время спада CAS# выполняется запись в ячейку. Переход WE# в низкий уровень и обратно при высоком уровне CAS# переводит выходной буфер EDO DRAM в высокоимпедансное состояние RASx# Стробы выборки строк. Сигналы RASO* и RAS1 # используются соответственно для бит [0:15] и [16:31] первого банка, RAS1#nRAS3#— для бит [0:15] и [16:31] второго банка 7.1. Динамическая память_____________________________________________ 261 Таблица 7.10.Сигналы модулей SIMM Сигнал Назначение

CAS1# — DQ[8:15], PQ1; CAS2# — DQ[16:23], PQ2; CAS3# — DQ[24:31], PQ3. В ECC-модулях возможно обращение только ко всему модулю по сигналам CASO* и CAS1 # CAS- Строб выборки столбцов для контрольных разрядов (редко используемый вариант) Parity* ОЕх# Output Enable — разрешение открытия выходного буфера. Эти выводы на системной плате обычно соединяются с логическим нулем, а для управления буфером используются сигналы RAS#, CAS# и WE#. На некоторых модулях SIMM могут отсутствовать PD[1:5] Presence Detect — индикаторы присутствия (обычно не используются) N.C. No Connection — свободный вывод

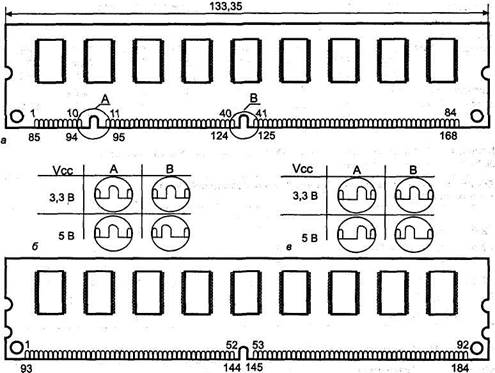

Модуль памяти DIMM-168 (Dual-In-line-Memory Module) имеет 168 независимых печатных выводов, расположенных с обеих сторон (контакты 1-84 — с фронтальной стороны, 85-168 — с тыльной). Разрядность шины данных — 8 байт, организация рассчитана на применение в компьютерах с четырех- и восьмибайтной шиной данных. Конструкция и интерфейс модулей соответствует стандарту JEDEC 21-С. Модули устанавливаются на плату вертикально в специальные разъемы (слоты) с ключевыми перегородками, задающими допустимое питающее напряжение и тип (поколение) применимых модулей. Модули выпускаются для напряжения питания 3,3 и 5 В. Вид модулей и сочетания ключей представлены на рис. 7.13. Толщина модулей с микросхемами в корпусах SOJ не превышает 9 мм, в корпусах TSOP - 4 мм. По внутренней архитектуре модули близки к SIMM-72, но имеют удвоенную разрядность и, соответственно, удвоенное количество линий CAS#. Также удвоено число сигналов разрешения записи и разрешения выходных буферов, что позволяет организовывать модули в виде двух 4-байтных банков с возможностью их чередования (Bank Interleaving). Модули могут иметь разрядность 64, 72 или 80 бит, дополнительные разряды 72-битных модулей организуются либо по схеме контроля паритета (приписываясь к соответствующим байтам), либо по схеме ЕСС; 80-битные — только по схеме ЕСС. Модули DIMM первого поколения (по IBM) были ориентированы на асинхронную память (FPM, EDO и BEDO); по архитектуре они напоминают SIMM-72. В модулях применяется параллельная идентификация — параметры быстродействия и объема передаются через 8 буферизованных выводов идентификации (Presence Detect pins). Модули первого поколения не получили широкого распространения, поскольку не принесли принципиальных новшеств в подсистему памяти. Модули второго поколения отличаются тем, что позволяют использовать микросхемы как асинхронной (FPM и EDO), так и синхронной динамической памяти Глава 7. Интерфейсы электронной'памяти (SDRAM). Внешне они похожи на модули первого поколения, но обличаются ключом, не допускающим ошибочную установку. Унифицированное назначение выводов позволяет в одни и те же слоты устанавливать как модули DRAM; так и SDRAM. Нумерация бит данных единая для всех типов организации — контрольные биты СВх имеют отдельную нумерацию, их наличие зависит от организации (паритет, ЕСС-72, ЕСС-80).

Рис. 7.13. Модули DIMM: а — вид модуля DIMM-168, б — ключи для модулей первого поколения, в — ключи для модулей второго поколения, г — вид модуля DIMM-184 Модули с любой организацией используют побайтное распределение информационных бит по сигналам CASx# (табл. 7.11), распределение контрольных бит представлено в табл. 7.12. Младший бит адреса приходит по одной линии на все микросхемы модуля. Сигналы управления модулей SDRAM значительно отличаются от модулей DRAM. Исполняемая операция SDRAM определяется сигнала* ми RAS#, CAS# и WE#, синхронизируемыми по фронту соответствующих сигналов СКх. Назначение сигналов модулей приведено в табл. 7.13, назначение выводов модулей DRAM — в табл. 7.14, SDRAM — в табл. 7.15. 7.1. Динамическая память Таблица 7.11.Организация информационных и управляющих сигналов для модулей DIMM-168 второго поколения

Таблица 7.12.Связь контрольных бит с управляющими сигналами для модулей DIMM-168 второго поколения

Таблица 7.13.Сигналы модулей DIMM-168 второго поколения и DIMM-184

продолжение*? 264________________________________ Глава 7. Интерфейсы электронной памяти Таблица 7.13(продолжение)

7.1. Динамическая память

Глава 7. Интерфейсы электронной памяти

Не нашли, что искали? Воспользуйтесь поиском по сайту: ©2015 - 2026 stydopedia.ru Все материалы защищены законодательством РФ.

|

Стандартизованная информация о микросхеме

Стандартизованная информация о микросхеме продолжение^

продолжение^ Модули SIMM-30, SIPP, SIMM-72

Модули SIMM-30, SIPP, SIMM-72

Контакт Назначение для модулей х32, Parity/ECC1

Контакт Назначение для модулей х32, Parity/ECC1

1 Модули ECC различных производителей могут отличаться по назначению выводов. Некоторые модули по выводам совпадают с паритетными, но могут различаться по связям контрольных бит с сигналами RASx# и CASx#.

1 Модули ECC различных производителей могут отличаться по назначению выводов. Некоторые модули по выводам совпадают с паритетными, но могут различаться по связям контрольных бит с сигналами RASx# и CASx#. MAi Multiplexed Address — мультиплексированные линии адреса. Во время спада сигнала RAS# на этих линиях присутствует адрес строки, во время спада CAS# — адрес столбца. Модули SIMM объемом 16 Мбайт могут быть с симметричной (square — квадратной) организацией — 11 бит адреса строк и 11 бит адреса колонок или асимметричной — 12x10 бит соответственно

MAi Multiplexed Address — мультиплексированные линии адреса. Во время спада сигнала RAS# на этих линиях присутствует адрес строки, во время спада CAS# — адрес столбца. Модули SIMM объемом 16 Мбайт могут быть с симметричной (square — квадратной) организацией — 11 бит адреса строк и 11 бит адреса колонок или асимметричной — 12x10 бит соответственно CASx# Стробы выборки столбцов, отдельные для каждого байта: CASO# — DQ[0:7], PQO;

CASx# Стробы выборки столбцов, отдельные для каждого байта: CASO# — DQ[0:7], PQO; Модули DIMM-168 и DIMM-184

Модули DIMM-168 и DIMM-184

В модулях SDRAM вместо раздельных сигналов RAS[0:3]# для выбора банков (рядов микросхем) используются сигналы S0#, S1#, S2# и S3#; вместо CAS[0:7]# для выбора байтов — сигналы DQMBO-DQMB7; сигналы WE2#, OEO# и ОЕ2# не используются.

В модулях SDRAM вместо раздельных сигналов RAS[0:3]# для выбора банков (рядов микросхем) используются сигналы S0#, S1#, S2# и S3#; вместо CAS[0:7]# для выбора байтов — сигналы DQMBO-DQMB7; сигналы WE2#, OEO# и ОЕ2# не используются.