|

|

Преимущества виртуального отображения страниц и адресное пространство процесса.Для защиты и виртуализации памяти в процессорах х86 предусмотрены два основных механизма: сегментация и страничная трансляция адресов. При сегментации операционная система выделяет каждому процессу сегменты — области памяти различного назначения, с разными правами доступа и разного размера. Из одних сегментов можно только читать данные, в другие возможна и запись. Для программного кода выделяются специальные сегменты, инструкции могут выбираться и исполняться только из них. По отношению к принципу хранимости программы это является искусственным ограничением для фон-неймановской машины, но целесообразность такого ограничения очевидна. Процессору «безразлично» содержимое ячейки памяти, на которую передалось управление, — он всегда пытается трактовать ее как код инструкции (или префикс). Если ошибочно передать управление на область данных, то дальнейшее поведение процессора непредсказуемо — это так называемый «вылет». Защита не позволяет передать управление на сегмент данных: сработает исключение защиты, которое обрабатывается операционной системой, и ошибочный процесс принудительно завершится. Таким образом, вероятность вылета снижается. Чтобы выдержать принцип хранимости программы, на время ее загрузки в память или программной модификации ту же область объявляют сегментом данных, в который разрешена запись. Система защиты может полностью контролировать распределение памяти, генерируя исключения в случаях различных нарушений. При страничной трансляции адресов (paging) виртуальная логическая память (для каждой виртуальной машины) делится на страницы одинакового (фиксированного) размера. Любая страница виртуальной логической памяти (адресуемой программой в пределах выделенных ей сегментов) может отображаться на любую область физической памяти (реально установленной оперативной). Отображение поддерживается с помощью специальных таблиц страничной трансляции адресов, в которых помимо записей, описывающих связи адресов, есть указания на присутствие/отсутствие страницы в физической памяти. Благодаря этому страница памяти, не нужная процессору в данный момент времени, может быть выгружена на устройство хранения (диск). На ее место можно загрузить нужную страницу. Заявку на загрузку нужной страницы делает сам процессор без каких-либо усилий со стороны выполняемой программы: если программе потребовалась ячейка виртуальной памяти из страницы, образа которой нет в физической памяти, вырабатывается специальное исключение. Обработчик этого исключения (это часть ОС) находит свободную физическую страницу (возможно, выгрузив на диск ту, которая, по его мнению, пока не нужна), «подкачивает» на нее с диска требуемую информацию и возвращает управление процессу, прерванному исключением. Этот процесс ничего «не заметит» (кроме некоторой задержки выполнения инструкций). Таким образом, в распоряжение всех процессов, исполняемых на компьютере псевдопараллельно, предоставляется виртуальная оперативная память, размер которой ограничен суммой объема физической оперативной памяти и области дисковой памяти, выделенной для подкачки страниц. В большинстве современных ОС механизм сегментации не используется из-за чрезмерной сложности. В них применяется плоская модель памяти (формально для всех целей определен один и тот же сегмент), а для организации виртуальной памяти и ее защиты (но не такой строгой) задействован механизм страничной трансляции адресов. ……………………………….. 2.2 Страничное управление памятью, виртуальная память.

Сраничное управление (Paging) является средством организации виртуальной памяти с подкачкой страниц по запросу (Demand-Paged Virtual Memory). В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация оперирует с памятью, как с набором страниц одинакового размера. В момент обращения страница может присутствовать в физической оперативной памяти, а может быть выгруженной на внешнюю (дисковую) память. При обращении к выгруженной странице памяти процессор вырабатывает исключение #PF — отказ страницы, а программный обработчик исключения (часть ОС) получит необходимую информацию для свопинга — «подкачки» отсутствующей страницы с диска. Страницы не имеют прямой связи с логической структурой данных или программ. В то время как селекторы можно рассматривать как логические имена модулей кодов и данных, страницы представляют части этих модулей. Учитывая обычное свойство локальности (близкого расположения требуемых ячеек памяти) кода и ссылок на данные, в оперативной памяти в каждый момент времени следует хранить только небольшие области сегментов, необходимые активным задачам. Эту возможность (а следовательно, и увеличение допустимого числа одновременно выполняемых задач при ограниченном объеме оперативной памяти) как раз и обеспечивает страничное управление памятью. В первых 32-разрядных процессорах (начиная с i80386) размер страницы составлял 4 Кбайт. Начиная с Pentium, появилась возможность увеличения размера страницы до 4 Мбайт, одновременно с использованием страниц размером 4 Кбайт. В Р6 имеется возможность расширения физического адреса до 36 бит (64 Гбайт), при котором могут использоваться страницы размером 4 Кбайт и 2 Мбайт.

Базовый механизм страничного управления использует двухуровневую табличную трансляцию линейного адреса в физический. Механизм имеет три части: каталог страниц (Page Directory), таблицы страниц (Page Table) и собственно страницы (Page Frame). Механизм включается установкой бита PG=1 в регистре CRO. Регистр CR2 хранит линейный адрес отказа (Page Fault Linear Address) — адрес памяти, по которому был обнаружен последний отказ страницы. Регистр CR3 хранит физический адрес каталога страниц (Page Directory Physical Base Address). Его младшие 12 бит всегда нулевые (каталог выравнивается по границе страницы).

Адресное пространство х86 х86 может работать с двумя типами адресов: 32-разрядным адресом, в котором 16 бит задают смещение в сегменте, 14 бит— номер сегмента и 2 бита используются для разных загадочных целей. При этом размер сегмента не более 64 Кбайт, а общий объем виртуальной памяти не превышает 1 Гбайта. 48-разрядным адресом, в котором смещение в сегменте занимает 32 бита. В этом случае размер сегмента может быть до 4 Гбайт, а общий объем виртуальной памяти до 244 байт. В обоих случаях сегмент может быть разбит на страницы по 4 Кбайт. При этом сегментная часть адреса и его смещение лежат в разных регистрах, и с ними можно работать раздельно. В реальном режиме возможность такой работы порождает весь "зоопарк моделей памяти", с которыми знакомы те, кто писал на С для MS DOS. В защищенном режиме х86 большинство систем программирования выделяют программе один сегмент с 32-разрядным смещением, и программа живет там так, будто это обычная машина с 32-разрядным линейным адресным пространством. Формат дескриптора сегмента в процессорах x86. Прикладные сегменты. Формат дескрипторной таблицы. Дескрипторы сегментов Имеется дескриптор сегмента, используемый для описания каждого сегмента в системе. Имеются обычные и системные дескрипторы. Ниже представлен дескриптор во всей своей красоте. Такой странный формат создан специально для того, чтобы обеспечить совместимость с 286. Заметьте, что он занимает 8 байт

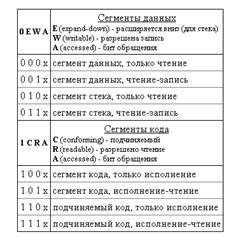

Разъяснения: R зарезервирован (0) DPL 0 означает ядро, 3 означает пользователя G 1 означает гарантировано 4К (В Linux установлен всегда) D 1 означает 32-х битное значение операнда по умолчанию U определяется программистом P 1 означает присутствие в физической памяти S 0 означает системный сегмент, 1 означает обычный сегмент кода или данных TYPE Существует много возможностей. Прерывания различны для системных и обычных дескрипторов. 3. Формат дескрипторной таблицы. На рисунке E.3. приведен формат дескрипторов в дескрипторных таблицах. Подробнее смотри [??? Григорьев и Обнинск.] На них обозначены:

Базовый адрес (32-х битный) - базовый адрес сегмента. Именно этот адрес сформирует процессор при нулевом смещении. Предел (20-битный). Определяет размер сегмента в байтах. Бит присутствия (P) установлен в состояние 1, когда он находится (присутствует) в физической памяти. Двухбитное поле привилегий (DPL) определяет уровень привилегий сегмента. Существуют четыре уровня привилегий: от 0 до 3. Бит S (системный, сегмент) всегда установлен в 1, если этот объект в дескрипторной таблице является сегментом. В случае S=0 данный объект может являться, а может и не являться сегментом памяти. Бит гранулярности G. При бите гранулярности G = 0 предел сегмента измеряется в байтах, а при G = 1 - в страницах по 4 Кбайт. Бит D - размер по умолчанию. Он определяет, какая из размерностей для данных (16 или 32 бита) применяется для операндов процессора. При D=0 процессор интерпретирует содержимое сегмента кода как 16-ти битный код процессора i80286, а при D=1 - как 32-х битный код процессора i80486 и старше. Использование бита D - самый простой способ переключения между 16-ти и 32-х битными приложениями. Бит A - доступа и обращения. Этот бит процессор автоматически устанавливает в состояние 1, когда происходит обращение к сегменту в физической памяти, описываемым данным дескриптором. Он предназначен для предотвращения свопинга сегмента на диск в момент обращения к нему. Бит X зарезервирован корпорацией Intel для своих будущих разработок. Он должен всегда равняться 0. Бит U может быть использован программистом для своих целей. Трехбитное поле ТИП используется для указания целевого использования сегмента. Его значения: 000b - сегмент данных, разрешено только считывание. 001b - сегмент данных, разрешено считывание и запись. 010b - сегмент стека, разрешено только считывание (не используется в практике.) 011b - сегмент стека, разрешено чтение и запись. 100b - сегмент кода, разрешено только выполнение. 101b - сегмент кода, разрешено выполнение и считывание. 110b - подчиненный сегмент кода, разрешено только выполнение. 111b - подчиненный сегмент кода, разрешено выполнение и считывание.

Не нашли, что искали? Воспользуйтесь поиском по сайту: ©2015 - 2026 stydopedia.ru Все материалы защищены законодательством РФ.

|