|

|

и программируемые аналоговые ИМСМЕТОДИЧЕСКИЕ УКАЗАНИЯ По проведению практического занятия №3 Тема занятия: СОСТОЯНИЕ И ПЕРСПЕКТИВЫ РАЗВИТИЯ ЭЛЕМЕНТНОЙ БАЗЫ СОВРЕМЕННОЙ РАДИОЭЛЕТРОННОЙ АППАРАТУРЫ (продолжение) Программируемые аналоговые матрицы и программируемые аналоговые ИМС Информация о первых электрически программируемых аналоговых матрицах (ПАМ) появилась в конце 90-х – начале 2000-х годов. Наиболее известными компаниями, которые объявили о начале их выпуска, были Motorola и Lattice Semiconductor (LS). Выпуск ПАМ серии MPAA с использованием МОП-технологии компания Motorola анонсировала в 1998 году. В настоящее время информация о производстве и продаже серии MPAA отсутствует. Это обстоятельство может быть связано с тем, что в 2000 году от фирмы Motorola отпочковалась компания Anadigm, о разработках которой речь пойдет несколько позднее. В 2001 году компанией LS (сайт www.lattice.semi.com) был организован выпуск нового семейства ПАМ типа ispPAC на МОП-структурах. Начиная с этого семейства за данными ПАМ, закрепилось название «программируемые аналоговые интегральные микросхемы» (ПАИС, в зарубежной терминологии Field Programmable Analog Array - FPAA). Базис чисто аналоговый: МОП-транзисторы, МОП-резисторы и МОП-конденсаторы. Следует подчеркнуть, что это не схемотехника на переключаемых МОП-конденсаторах. В семейство ПАМ типа ispPAC входят ispPAC10, ispPAC20 и ispPAC80. Дадим расшифровку этой англоязычной аббревиатуры: In-System Programmable Analog Circuit. Указание. Здесь нужно предложить студентам освежить в памяти необходимую информацию о перечисленных выше МОП-компонентах, в частности, характеристики и параметры МОП-транзисторов различных типов, варианты выполнения МОП-резисторов, а также принципы реализации и основные параметры МОП-конденсаторов и МОП-ключей. ПАИС типа ispPAC10 содержит четыре макроячейки, которые именуются PAC-блоками. Изобразим упрощенную схему одной макроячейки (рис. 3.1). Она состоит из двух инструментальных усилителей (ИУ) и одного выходного усилителя, реализованного по схеме сумматора-интегратора на базе интегрального операционного усилителя (ОУ). При этом выходы двух ИУ соединены с суммирующим входом ОУ.

Рис. 3.1. Упрощенная схема макроячейки Условное обозначение входного инструментального усилителя приведено на рис. 3.2.

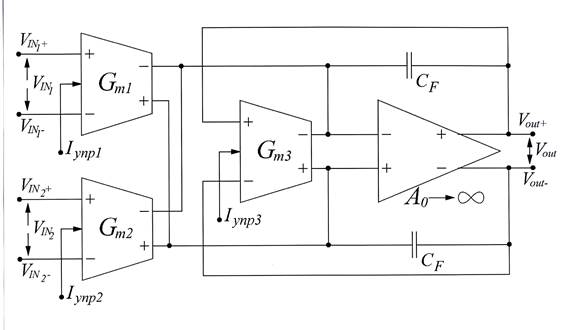

Рис. 3.2. Условное обозначение полностью дифференциального ОТУ Такой тип ОУ называют операционным транскондуктивным усилителем (ОТУ), причем с высокоомными полностью дифференциальными входом и выходом, что позволяет эффективно подавлять синфазные помехи. Данный усилитель относится к классу источников тока, управляемых напряжением (ИТУН), и характеризуется, в первую очередь, крутизной (проводимостью) Gm. Значение Gm может программироваться путем изменения управляющего тока Iупр в пределах 20мкСм…200мкСм (10 шагов). На рис. 3.3 изображена полная схема макроячейки. В ней использованы три транскондуктивных, полностью дифференциальных ОУ типа ИТУН и один полностью дифференциальный ОУ типа источник напряжения, управляемый напряжением (ИНУН). Конденсаторная матрица СF состоит из семи конденсаторов и позволяет получить 27=128 возможных номиналов реализуемой емкости, что соответствует более 120 дискретным значениям в частотном диапазоне 10…100 кГц с точностью ±5%. Коэффициент усиления входных усилителей программируется в диапазоне ±1…±10.

Рис. 3.3. Полная схема макроячейки Здесь имеется система автокалибровки (auto-call), которая позволяет разрабатывать высокоточные частотные фильтры и усилители, а также упростить и ускорить процесс проектирования и настройки опытного образца. В состав ispPAC10 входит также источник опорного напряжения (ИОН) с номиналом 2,5 В. ПАИС типа ispPAC20 содержит две макроячейки, ИОН, восьмиразрядный ЦАП и два компаратора. В макроячейке также программируются коэффициент усиления ИУ в диапазоне от -10 до +10 с шагом, равным 1, величина емкости конденсатора обратной связи CF в выходном усилителе (128 возможных значений номинала этой емкости) и режим включение/выключение обратной связи в выходном усилителе ячейки. Средства внутренней трассировки с помощью коммутируемых МОП-ключей позволяют выполнить требуемые соединения между входными контактами ИМС, входами и выходами макроячеек, выходом ЦАП и входами компараторов. Объединение нескольких макроячеек дает возможность реализовать схемы перестраиваемых активных фильтров, основанных на использовании звена интегратора, в диапазоне частот от 10 кГц до 100 кГц. Погрешность установки частоты полюса не более 5%. ПАИС типа ispPAC80 содержит входной инструментальный усилитель транскондуктивного типа, выходной ОУ, активный фильтр пятого порядка с программируемыми характеристиками, а также блоки управления и соединения, аналогичные предыдущим сериям. Все указанные ИМС питаются от источника с напряжением +5 В. Величины тока потребления: · 23 мА для ispPAC10; · 21 мА для ispPAC20; · 19 мА для ispPAC80. Проектирование устройств серии ispPAC поддерживается САПР типа PAC Designer. Демонстрационную версию PAC Designer можно переписать с сайта компании LS (за исключением возможности выполнения режима конфигурации ИМС). Компания Lattice Semiconductor не является единственным производителем ПАИС. Так, компания Fast Analog Solution (сайт www.fas.co.uk) предлагает такие ИМС в серии TRAC. Фирма обозначает их как FPAD (Field Programmable Analog Devices). Например, ПАИС TRAC020 содержит 20 макроячеек, каждая из которых имеет в своем составе ОУ и конфигурируемые цепи линейной и нелинейной обратной связи. В качестве реактивного элемента здесь выступает конденсаторная матрица. Это позволяет реализовывать основные базовые узлы аналоговой обработки сигналов, в частности, масштабные усилители, интеграторы, дифференциаторы, а также функциональные преобразователи типа амплитудных ограничителей, логарифмических усилителей и выпрямителей. Следует отметить, что эта компания также поставляет программное обеспечение, которое обладает достаточно широкими возможностями по вводу параметров и схемотехническому моделированию функциональных устройств. Еще один известный производитель ПАИС – компания Anadigm (сайт www.anadigm.com), которая выделилась из компании Motorola в 2000 году. Эта фирма является лидером в производстве ПАИС и выпускает их несколько типов. Один из первых – AN10E40. Такая ПАИС имеет некоторое множество макроячеек, каждая из которых выполнена по МОП-технологии с использованием схемотехники на переключаемых МОП-конденсаторах (рис. 3.4).

Рис. 3.4. Структурная схема ПАИС типа AN10E40

Подробно мы обсудим вопросы построения таких аналого-дискретных ПАИС и проектирования на их основе п/з БИС в последнем разделе нашего курса, когда вы получите необходимый объем знаний по такой схемотехнике. Существуют также аналого-цифровые ПАИС, в которых на одном кристалле располагаются аналоговые элементы, программируемая логика и микроконтроллерное ядро. К таким, по существу, простейшим «системам на одном кристалле» (System on chip) относятся изделия компании SIDSA (сайт www.sidsa.com). Каждая ПАИС такого типа (рис. 3.5) содержит программируемый аналоговый блок, который включает в себя четыре дифференциальных канала.

Рис.3.5. Структурная схема аналого-цифровой ПАИС

В свою очередь, каждый канал состоит из трех ОУ с программируемым коэффициентом усиления и четырех компараторов с программируемым источником опорного напряжения. Кроме того, в состав аналогового блока входят четыре АЦП с конфигурируемой разрядностью от 8 до 10 бит и быстродействием до 800000 отсчетов в секунду. Используемая программируемая логика также обладает высоким быстродействием (до 40 МГц). Микроконтроллерное ядро по своим параметрам и характеристикам совместимо с ядром типа 8051 компании Intel. В состав поставки такой ПАИС входит также специализированное программное обеспечение, позволяющее осуществить ввод проекта, моделирование и конфигурирование п/з БИС. Современные сложные электронные устройства физически реализуются в виде систем на кристалле (System on Chip - SoC). В самом общем случае в структуре СБИС данного типа можно выделить три составные части: · входная высокочастотная интерфейсная часть, в которой производится прием и предварительная обработка аналоговых радиосигналов; · устройство сопряжения аналоговой интерфейсной части с цифровой, представляющее собой некоторую совокупность аналого-цифровых преобразователей; · цифровая часть, в которой реализуется заданный алгоритм цифровой обработки сигналов. Элементный базис цифровой части составляют так называемые IP (intellectual property) – блоки, которые представляют собой достаточно сложные БИС, например, сигнальные процессоры, микроконтроллеры, запоминающие устройства и др., содержащие оригинальные архитектурные, схемотехнические и топологические решения. Однако такая структура SoC порождает большую проблему, связанную с обеспечением правильного функционирования входной интерфейсной части, поскольку цифровая часть, в которой производится обработка цифровых сигналов, становится источником достаточно интенсивных импульсных помех. В заключение следует отметить, что проектирование ИМС высокой степени интеграции, в том числе БИС и СБИС, осуществляется с помощью специальных программных средств, которые, как правило, разработаны зарубежными компаниями: Cadence, Synopsys и Mentor Graphics.

Список рекомендуемой литературы 1. Казеннов Г.Г. Основы проектирования интегральных схем и систем / Г.Г. Казеннов.-М.: БИНОМ. Лаборатория знаний, 2009.- 295 с.

Не нашли, что искали? Воспользуйтесь поиском по сайту: ©2015 - 2024 stydopedia.ru Все материалы защищены законодательством РФ.

|