|

|

Синхронизация и последовательность действий МП

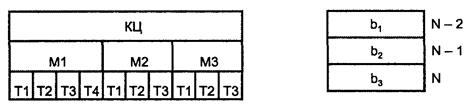

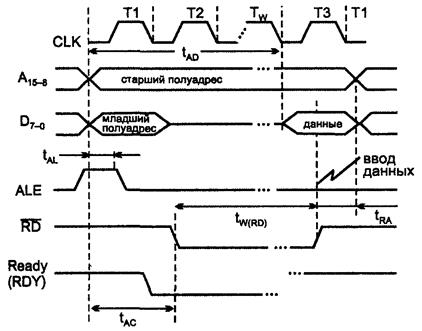

При естественном следовании команд МП, начав работу, выбирает из памяти и выполняет одну команду за другой, пока не дойдет до команды Микропроцессор К1821 имеет следующие типы машинных циклов: 1. Выборки команды (OF, Opcode Fetch). 2. Чтения из памяти (MR, Memory Read). 3. Записи в память (MW, Memory Write). 4. Чтения из ВУ (IOR, Input-Output Read). 5. Записи в ВУ (IOW, Input-Output Write). 6. Подтверждения прерывания (INA, Interrupt Acknowledge). 7. Освобождения шин (BI, Bus Idle). 8. Останов (HALT). В начале каждого машинного цикла генерируются сигналы состояния, идентифицирующие тип цикла и действующие в течение всего цикла. Функции выводов и сигналов: q A15-8 - выходные линии с тремя состояниями для выдачи старшего бай- q AD7-0 - двунаправленные мультиплексированные линии с тремя состояниями для выдачи младшего байта адреса памяти или полного адреса ВУ в первом такте машинного цикла, после чего используются как шина данных. Как видно из сказанного, при адресации ВУ адресная информация обеих полушин (A15-8 и AD7-0) дублируется; q ALE - строб разрешения загрузки младшего байта адреса памяти во внешний регистр для его хранения в течение машинного цикла. Появляется в первом такте машинного цикла. Регистр загружается задним фронтом сигнала ALE; q RD, WR - стробы чтения или записи. Низкий уровень соответствующего сигнала свидетельствует о том, что адресованная ячейка памяти или q READY - входной сигнал, показывающий, что память или ВУ готовы к q S1, S0 - сигналы состояния МП, сообщаемые внешней среде. Формируются в начале и сохраняются во время всего машинного цикла; q IO/М - сигнал выбора памяти или внешнего устройства. При высоком Совместно с сигналами S1, S0 сигнал Ю/М идентифицирует тип машинного цикла. Сигналы состояния и управляющие сигналы RD, WR и Таблица 5.1

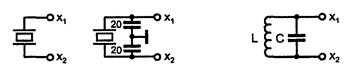

В приведенной таблице через ТС обозначено третье состояние. q x1, x2 - эти выводы присоединяются к кварцевому резонатору или другим частотно-задающим цепям для обеспечения работы внутреннего генератора синхроимпульсов МП. Частота на выводах x1, x2 в 2 раза выше рабочей частоты; q RESIN (RESET IN) - вход сигнала сброса МП в начальное состояние. Сигнал может поступить в любое время по команде оператора. Автоматически формируется при включении питания. Под его воздействием сбрасываются регистры PC и IR, триггеры разрешения прерывания, подтверждения захвата и др.; q CLK - выход синхроимпульсов для микропроцессорной системы. Частота этих импульсов в два раза ниже частоты на выводах x1, x2; q RESET - выходной сигнал сброса для внешних модулей системы, привязанный к тактовым импульсам CLK, т. е. отличающийся от сигнала RESIN по фазе; q INTR (Interrupt Request) - вход запроса векторного прерывания, вызывающий генерацию строба INTA, если прерывание разрешено программой. Адрес подпрограммы, вызываемой этим входом, выдается внешним устройством. При сбросе прием сигнала запрещается (прерывания запрещены); q INTA (Interrupt Acknowledge) - выход строба подтверждения векторного q RST 5,5; RST 6,5; RST 7,5 - входы запросов радиального прерывания типа RSTn (n = 5,5; 6,5; 7,5). Начальные адреса подпрограмм обслуживания равны 8n. Приоритеты фиксированы, высший приоритет у входа RST 7,5. Приоритеты всей группы запросов выше приоритета запроса INTR. Запросы маскируемые, причем независимо друг от друга; q TRAP - вход запроса, немаскируемого прерывания, имеющий максимальный приоритет; q SID, SOD (Serial Input Data, Serial Output Data) - вход и выход последовательной передачи данных. По команде RIM входной бит загружается в старший разряд аккумулятора, по команде SIM выводится из этого разряда; q HOLD - сигнал запроса захвата шин. Формируется внешним устройством; q HLDA - сигнал подтверждения захвата (Hold Acknowledge). Является ответом на сигнал HOLD, формируемым в конце текущего машинного цикла. Свидетельствует об отключении МП от системных шин. При этом шины и линии управляющих сигналов RD, WR, IO/М и ALE переводятся в третье состояние.

а)

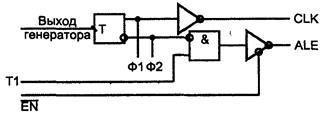

б) Рис. 5.3.Внешние элементы тактового генератора (а) Выводы x1 и x2, предназначенные для создания совместно с внутренними элементами МП генератора тактовых импульсов, могут быть использованы Для образования сигналов синхронизации CLK выход генератора подается Сигнал ALE формируется как один импульс последовательности Ф1, выделяемый из нее в первом такте (Т1) каждого машинного цикла. Буфер выдачи сигнала ALE во внешние цепи имеет вход разрешения EN. Частота синхросигналов МП в два раза ниже частоты генератора. Командный циклКЦ (рис. 5.4,а) начинается с выборки команды (Opcode Если команда трехбайтная, то она хранится в памяти так, как показано на

а) б) Рис. 5.4. Циклы и такты микропроцессора К1821ВМ85А (а) и пример размещения команды в памяти микропроцессорной системы (б) Таблица 5.2

После выборки и декодирования команды могут понадобиться дополнительные машинные циклы для ее выполнения. Всего в командном цикле может быть от одного до пяти машинных циклов. Машинный циклсостоит из тактов, в которых выполняются типовые действия, рассмотренные ниже. Число тактов в различных машинных циклах - В командном цикле может содержаться от 4 до 18 тактов. Сигналы, реализующие тот или иной МЦ, генерируются блоком управления МП на основании информации, содержащейся в первом байте команды. Проиллюстрируем сказанное примером выполнения команды STA b3b2 Каждый машинный цикл делится на такты(состояния) - интервалы между одноименными фронтами тактовых импульсов. Типовые действия, выполняемые в тактах машинного цикла: q Т1 Адрес памяти или ВУ выставляется на AD7-0 и A15-8, генерируется сигнал ALE для фиксации битов AD7-0. На линиях IO/M, S1 и S0 выставляется информация, определяющая тип цикла. Проверяется флаг HALT. q Т2 Проверяются входы Ready и Hold. Программный счетчик инкрементируется, если данный машинный цикл есть часть выборки команды. Во всех машинных циклах кроме цикла ВI (освобождения шин) один из управляющих стробов RD, WR или INTA переходит из единичного состояния в активное нулевое. q TW Появляется при неготовности памяти или ВУ к обмену (на линии READY низкий уровень напряжения). Состояния линий адресов, данных и управления остаются теми же, что и в конце такта. Сигнал READY проверяется в каждом такте ожидания. q Т3 Байт команды или данных передается в микропроцессор или из него. q Т4 Декодируется содержимое регистра команд. q T5,6 Используются при необходимости для завершения некоторых команд. Системные шины не используются.

Рис. 5.5. Временные диаграммы цикла чтения микропроцессора

Машинный цикл всегда содержит такты T1…Т3, иногда имеет большее число тактов, но для чтения или записи требуется только три такта. Временные Система прерываний

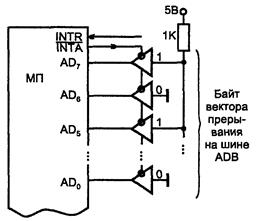

При работе МП системы могут произойти события, требующие немедленной реакции. Такая реакция обеспечивается прерыванием программы и переходом к обслуживанию источников запросов на прерывание. Внутри системы запросы возникают при сбоях в работе, переполнении разрядной сетки, попытке деления на нуль и т. д. Извне могут поступать сигналы аварийных ситуаций в управляемых объектах, неисправности источников питания и др. Когда ВУ нуждается в обслуживании, оно устанавливает триггер запроса прерывания, и сигнал запроса сохраняется, пока не будет воспринят и обработан микропроцессором. В ответ на принятый запрос прерывания в микропроцессорной системе завершается выполнение текущей команды, запоминается состояние МП, выполняется подпрограмма обслуживания прерывания, восстанавливается состояние МП, и затем возвращается управление соответствующей команде основной программы. Микропроцессор К1821 имеет пять входов прерывания и один выход управления им INTA. Прерывание должно ввести в действие команду CALL, согласно которой состояние программного счетчика PC передается в стек, а в Входы МП, связанные с прерываниями, называются TRAP; RST 5,5; RST 6,5; RST 7,5; INTR. При организации прерываний решаются задачи маскирования запросов и определяются их уровни приоритета при конфликтах из-за одновременного поступления нескольких запросов. Маскированиесостоит в запрещении действия соответствующего входа. Входы запросов прерывания могут быть маскируемыми или не маскируемыми, Вход TRAP является немаскируемым и имеет наивысший приоритет. Он не может быть запрещен командами программы. К этому входу подключают сигналы, оповещающие о наиболее важных событиях в микропроцессорной Начальный адрес подпрограммы обслуживания прерывания TRAP размещен в фиксированной ячейке памяти с адресом 24Н. Таким образом, появление запроса прерывания по входу TRAP независимо ни от чего вызовет соответствующее прерывание после завершения выполнения текущей команды. Обозначение входов RSTn (n = 5,5; 6,5; 7,5) происходит от слова Restart. Напомним, что вектором прерываний называют информацию, необходимую для перехода к соответствующей подпрограмме обслуживания, в простейшем случае это просто начальный адрес прерывающей подпрограммы. Вход RST 7,5 является динамическим, реагирует на положительный фронт При поступлении запроса по входу INTR (Interrupt) вектор прерывания

Рис. 5.6.Аппаратная реализация пересылки байта при выполнении операции рестарта Сигнал INTA при этом поступает на входы разрешения выхода буферных Во время обработки прерываний, пока не выполнится команда EI, запрещаются другие прерывания кроме TRAP. Немаскируемое же прерывание 6. КОМАНДЫ МИКРОПРОЦЕССОРА

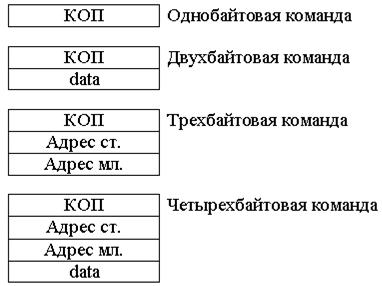

Команды микропроцессора в отличие от микрокоманд разрабатываются независимо от аппаратуры микросхемы, поэтому их разрядность обычно совпадает с разрядностью микропроцессора. Команда микропроцессора состоит из инструкции и обозначается код операции КОП (или INS в англоязычной литературе). Команда микропроцессора может состоять только из кода операции, когда не требуется указывать адрес операнда (операнды это данные, над которыми команда производит какое либо действие), или может состоять из кода операции и адресов операндов или данных. Форматы команд очень сильно зависит от структуры процессора. Рассмотрим построение команд для восьмиразрядного процессора. Примеры построения команд для такого процессора приведены на рис. 6.1.

Рис. 6.1. Форматы различных команд микропроцессора

Если для кода операции используется восьмибитное слово (байт), то при помощи этого слова можно закодировать 256 операций. В процессе разработки системы команд для операции может быть назначен любой код. Именно системой команд и определяется конкретное семейство процессоров. Однобайтовые команды позволяют работать с внутренними программно доступными регистрами процессора. Для выполнения одной и той же операции над разными регистрами процессора назначаются разные коды. Запоминать эти коды очень утомительно для человека. При программировании в машинных кодах легко совершить ошибку и очень трудно найти её, особенно если коды различаются только на один бит. Для сокращения объёма записи вместо двоичного можно воспользоваться шестнадцатиричным кодом, однако это не увеличивает наглядности программы. Фрагмент исполняемого кода микропроцессора приведён на рис. 6.2.

Рис. 2. Фрагмент исполняемого кода микропроцессора

Чтобы уменьшить объём запоминаемой информации и увеличить наглядность исходного текста программы, каждой операции процессора придумывают мнемоническое обозначение. В качестве мнемонического обозначения операции обычно используют сокращения английских слов, обозначающих эту операцию. Например: § для операции копирования используется мнемоническое обозначение MOV; § для операции суммирования используется мнемоническое обозначение ADD; § для операции вычитания используется мнемоническое обозначение SUB; § для операции умножения используется мнемоническое обозначение MUL и т.д. Для полного обозначения команды используется мнемоническое обозначение операции и используемые ею операнды, которые перечисляются через запятую. При этом в большинстве процессоров операнд приёмник информации записывается первым, а операнд источник информации вторым. Например: MOV R0, A ; Скопировать содержимое регистра A в регистр R0. ADD A, R5 ; Просуммировать содержимое регистров R5 и A, результат поместить в регистр A. Приведённые выше команды - это однобайтовые команды, так как в них используются только внутренние регистры процессора. Если в команде используется константа в качестве операнда или указывается адрес операнда в системной памяти, то команда будет занимать в системной памяти два или три байта. Например: MOV A, 1025 ; Скопировать содержимое 1025 ячейки памяти в регистр A. ADD A, #110 ; Просуммировать содержимое регистра A с числом 110.

Несмотря на то, что общий объём исходного текста программы увеличивается, скорость написания и особенно отладки программ в таком виде возрастает. Теперь вместо одного текста программы в памяти компьютера или на бумаге придется хранить два текста: один для человека, который в дальнейшем будем называть исходным текстом программы; другой для микропроцессора, который в дальнейшем будем называть загрузочным модулем. Преобразование программы, записанной в мнемоническом виде, в машинные коды является рутинной работой, которую можно поручить компьютерной программе. Язык программирования в котором для обозначения машинных команд используются мнемонические обозначения называется ассемблером. Точно так же называют и программу или пакет программ, которая осуществляет трансляцию (преобразование) исходного текста программы (исходный модуль) в машинные коды (загрузочный модуль).

7. СИСТЕМНАЯ ШИНА МИКРОПРОЦЕССОРА

7.1. Понятие системной шины микропроцессора 7.2. Адресное пространство микропроцессорного устройства 7.3. Способы расширения адресного пространства микропроцессора

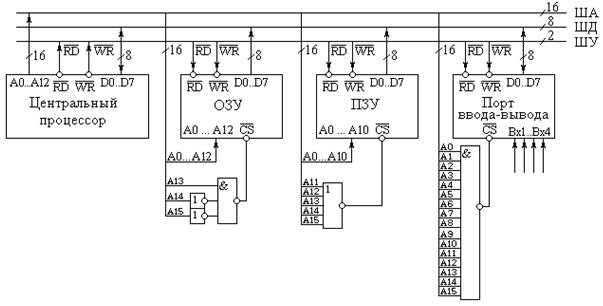

7.1. Понятие системной шины микропроцессора Системная шина микропроцессорапредназначена для обмена информацией микропроцессора с любыми внутренними устройствами микропроцессорной системы (контроллера или компьютера). В качестве обязательных устройств, которые входят в состав любой микропроцессорной системы, можно назвать ОЗУ, ПЗУ, таймер и порты ввода-вывода. Структурная схема простейшего микропроцессорного устройства приведена на рис. 7.1. В состав системной шины в зависимости от типа процессора входит одна или несколько шин адреса, одна или несколько шин данных и шина управления. Несколько шин данных и адреса применяется для увеличения производительности процессора и используется только в сигнальных процессорах. В универсальных процессорах и контроллерах обычно применяется одна шина адреса и одна шина данных. В понятие шины вкладывают разное значение при рассмотрении различных вопросов. В простейшем случае под понятием шина подразумевают параллельно проложенные провода, по которым передаётся двоичная информация. При этом по каждому проводу передаётся отдельный двоичный разряд. Информация может передаваться в одном направлении, как, например, для шины адреса или шины управления, или в различных направлениях (для шины данных). По шине данных информация передаётся либо к процессору, либо от процессора в зависимости от операции записи или чтения, которую в данный момент осуществляет процессор. В любом случае все сигналы, необходимые для работы системной шины формируются микросхемой процессора как это рассматривалось при изучении блока обработки данных. Иногда для увеличения скорости обработки информации функции управления системной шины берёт на себя отдельная микросхема (например, контроллер прямого доступа к памяти или сопроцессор). Арбитраж доступа к системной шине при этом осуществляет контроллер системной шины (в простейшем случае достаточно сигнала занятости шины). В некоторых случаях в понятие шина дополнительно включают требования по уровням напряжения, которыми представляются нули и единицы, передаваемые по её проводам. В состав требований могут быть включены длительности фронтов передаваемых сигналов, типы используемых разъёмов и их распайка, последовательность передаваемых сигналов и скорость их передачи.

Рис. 7.1. Структурная схема подключения микропроцессорных устройств к системной шине

При подключении различных устройств к системной шине возникает вопрос - как различать эти устройства между собой? Единственный способ сделать это использовать индивидуальный адрес для каждого устройства, подключенного к системной шине микропроцессора. Так как адресация производится к каждой ячейке устройства индивидуально, то возникает понятие адресного пространства, занимаемого каждым устройством и адресного пространства микропроцессорного устройства в целом.

7.2. Адресное пространство микропроцессорного устройства

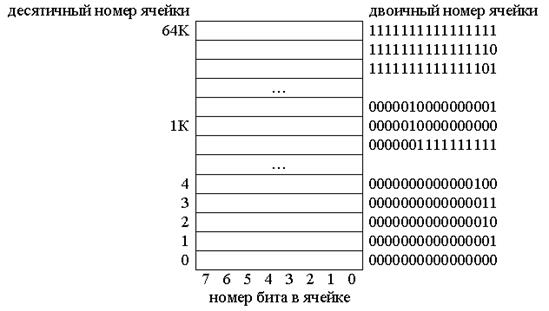

Адресное пространство микропроцессорного устройства изображается графически прямоугольником, одна из сторон которого представляет разрядность адресуемой ячейки этого микропроцессора, а другая сторона - весь диапазон доступных адресов для этого же микропроцессора. Обычно в качестве минимально адресуемой ячейки памяти выбирается восьмиразрядная ячейка памяти (байт). Диапазон доступных адресов микропроцессора определяется разрядностью шины адреса системной шины. При этом минимальный номер ячейки памяти (адрес) будет равен 0, а максимальный определяется из формулы:

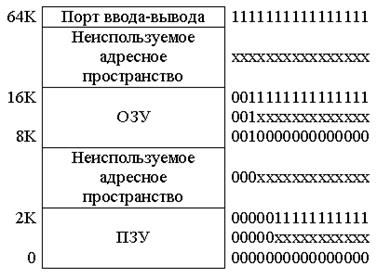

Для шестнадцатиразрядной шины это будет число 65535 (64K). Адресное пространство этой шины и распределение памяти микропроцессорной системы, изображённой на рис. 7.1, приведено на рис. 7.2, а распределение памяти микропроцессорной системы, изображённой на рис. 7.1, приведено на рис. 7.3.

Рис. 7.2. Адресное пространство шестнадцатиразрядной шины адреса

Рис. 7.3. Распределение памяти микропроцессора с шестнадцатиразрядной шиной адреса

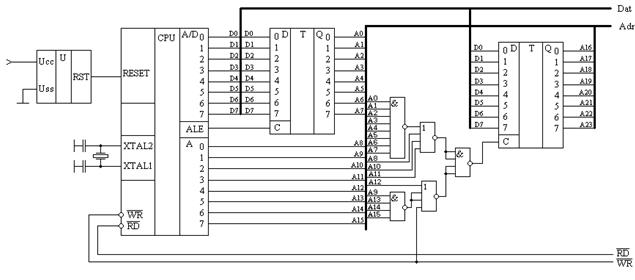

Микропроцессоры после включения питания и выполнения процедуры сброса всегда начинают выполнение программы с определённого адреса, чаще всего нулевого. Однако есть и исключения. Например, процессоры, на основе которых строятся универсальные компьютеры IBM PC или Macintosh стартуют не с нулевого адреса. Программа должна храниться в памяти, которая не стирается при выключении питания, то есть в ПЗУ. Выберем для построения микропроцессорной системы микросхему ПЗУ объёмом 2 килобайта, как это показано на рис. 7.1. При рассмотрении построения блока обработки сигналов мы договорились, что процессор после сброса начинает работу с нулевого адреса, поэтому разместим ПЗУ в адресном пространстве начиная с нулевого адреса. Для того, чтобы нулевая ячейка ПЗУ оказались расположенной по нулевому адресу адресного пространства микропроцессора, старшие разряды шины адреса должны быть равны 0. При построении схемы необходимо декодировать старшие пять разрядов адреса (определить, чтобы они были равны 0). Это выполняется при помощи дешифратора адреса, который в данном случае вырождается в пятивходовую схему "ИЛИ-НЕ" Это связано с тем, что внутри ПЗУ уже есть одиннадцативходовый дешифратор адреса. При использовании дешифратора адреса, обращение к ячейкам памяти выше двух килобайт не приведёт к чтению ячеек ПЗУ, так как на входе выбора кристалла CS уровень напряжения останется высоким. Теперь подключим микросхему ОЗУ. Для примера выберем микросхему объёмом 8 Кбайт. Для выбора любой из ячеек этой микросхемы достаточно тринадцатибитового адреса, поэтому необходимо дополнительно декодировать три оставшихся разряда адреса. Так как начальные ячейки памяти адресного пространства уже заняты ПЗУ, то использовать нельзя. Выберем следующую комбинацию цифр 001 и используем известные нам принципы построения схемы по произвольной таблице истинности. Дешифратор адреса выродится в данном случае в трёхвходовую схему "И-НЕ" с двумя инверторами на входе. Схема этого дешифратора приведена на рис. 7.1. Приведённый дешифратор адреса обеспечивает нулевой уровень сигнала на входе CS только при комбинации старших бит 000. Обратите внимание, что так как объём ПЗУ меньше объёма ОЗУ, то между областью адресов ПЗУ и областью адресов ОЗУ образовалось пустое пространство неиспользуемых адресов памяти. И, наконец, так как все микропроцессоры предназначены для обработки данных, поступающих извне, то в любой микропроцессорной системе должны присутствовать порты ввода-вывода. Порт ввода-вывода отображается в адресное пространство микропроцессорного устройства как одиночная ячейка памяти, поэтому порт ввода вывода можно разместить по любому свободному адресу. Проще всего построить дешифратор числа FFFFh. В этом случае дешифратор превращается в обычную 16-ти входовую схему "И-НЕ", поэтому и выберем эту ячейку памяти в адресном пространстве микропроцессора для размещения порта ввода-вывода.

7.3. Способы расширения адресного пространства микропроцессора

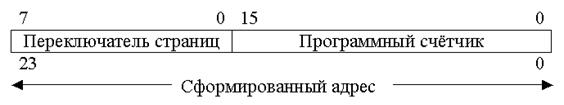

Известно, что размер адресного пространства определяется разрядностью счётчика команд микропроцессора. Достаточно часто при развитии микропроцессорной системы возможности адресного пространства исчерпываются. В таком случае приходится прибегать к методам расширения адресного пространства. Для расширения адресного пространства можно воспользоваться параллельным портом. Внешние выводы параллельного порта при этом используются в качестве старших битов адресной шины. Такой метод расширения адресного пространства называется страничным методом адресации. Регистр данных параллельного порта при использовании его для расширения адресного пространства будет называться переключателем страниц. Схема использования параллельного порта в качестве переключателя страниц памяти приведена на рис. 7.4.

Рис. 7.4. Использование параллельного порта в качестве переключателя страниц памяти.

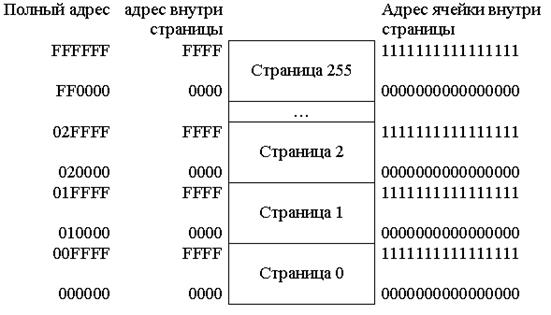

В этой схеме параллельный порт используется в качестве простейшего контроллера памяти микропроцессорного устройства. При применении восьмиразрядного параллельного порта в микропроцессорной системе появились дополнительные восемь линий адреса. В результате адресное пространство микропроцессорной системы увеличилось до 16 Мегабайт. Структура нового адресного пространства приведена на рис. 7.5, а принцип формирования нового адреса с использованием переключателя страниц приведён на рис. 7.6.

Рис. 7.5. Структура страничного адресного пространства

Рис. 7.6. Формирование адреса с использованием переключателя страниц

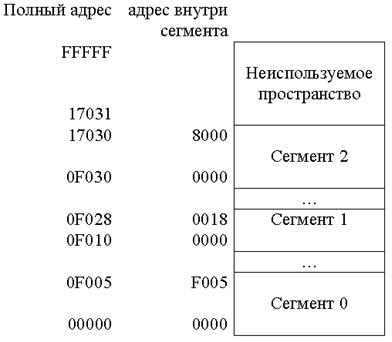

Метод страничной адресации прост в реализации и при формировании адреса физической памяти не приводит к дополнительным временным задержкам, но при использовании многозадачного режима работы процессора для каждой активной задачи выделяется целая страница в системной памяти микропроцессора. При такой работе в системной памяти процессора остаётся много неиспользуемых областей. Решить возникшую проблему позволяет метод сегментной организации памяти. При сегментном методе организации памяти для расширения адресного пространства используется базовый регистр, относительно которого производится адресация команд или данных в программе. Разрядность базового регистра обычно выбирают равной разрядности счётчика команд. В качестве базового регистра, как и при страничной организации памяти, можно использовать параллельный порт. Для формирования физического адреса используется параллельный двоичный сумматор. На входы этого сумматора подаётся содержимое базового регистра и содержимое счётчика команд. Суммирование производится со смещением содержимого базового регистра влево на несколько бит относительно счётчика команд (рис. 7.8). В результате максимальный размер сегмента определяется разрядностью программного счётчика, а максимальная неиспользуемая область памяти – смещением базового регистра относительно программного счётчика. Адресное пространство при использовании сегментного метода адресации приведено на рис. 7.7.

Рис. 7.7. Пример адресного пространства с разделением на сегменты

Количество сегментов определяется количеством базовых регистров. Сегменты могут перекрываться в адресном пространстве, и тем самым может регулироваться размер памяти, который отводится под каждый конкретный сегмент памяти. В компьютерах семейства IBM PC имеются четыре базовых регистра, определяющих сегмент данных, сегмент программы, сегмент стека и дополнительный сегмент. Информацию в базовые регистры заносит операционная система при переключении задач.

Рис. 7.8. Формирование адреса при сегментной адресации

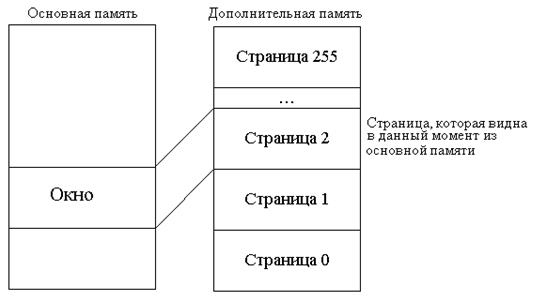

Ещё одним распространённым способом увеличения адресного пространства является применение окон. При использовании окон производится расширение не всего адресного пространства, а только его части. Внутри адресного пространства выделяется некоторая область, которая называется окном. В это окно может отображаться часть другого адресного пространства. При использовании окон может быть использован как страничный метод отображения адресного пространства, так и сегментный метод отображения адресного пространства в окно. При использовании страничного метода отображения, конкретная страница другого адресного пространства, которая в данный момент отображается в окно памяти, определяется переключателем страниц, построенному по такому же принципу как это было рассмотрено на рис. 7.4. При использовании сегментного метода отображения, конкретная область адресного пространства, которая будет отображаться в окно, определяется содержимым базового регистра. Если разрядность адреса вспомогательного адресного пространства, отображаемого в окно основной памяти, совпадает с разрядностью базового регистра, то любая область вспомогательной памяти может быть отображена в основную память с точностью до байта. Принцип построения оконной адресации при отображении страниц показан на рис. 7.9. Оконная адресация часто используется при развитии микропроцессорных семейств, когда размера областей памяти, отведённых для конкретных задач в младших моделях семейства, не хватает для старших моделей семейства, а при этом нужно поддерживать аппаратную совместимость с младшими моделями семейства. В качестве примера можно привести микросхемы I81c96 фирмы INTEL или TMS320c5410 фирмы Texas Instrument, где для расширения области регистров специальных функций используется оконная адресация.

Рис. 7.9. Применение окна для расширения адресного пространства 8. ПАРАЛЛЕЛЬНЫЙ ПОРТ

Параллельные портыпредназначены для обмена информацией микропроцессора с внешними устройствами, при этом в качестве внешнего устройства может использоваться другой компьютер. Параллельные порты позволяют согласовывать низкую скорость работы внешнего устройства и высокую скорость работы системной шины микропроцессора. С точки зрения внешнего устройства порт представляет собой обычный источник или приемник информации со стандартными цифровыми логическими уровнями (обычно ТТЛ), а с точки зрения микропроцессора - это ячейка памяти, в которую можно записывать данные или в которой сама собой появляется информация. В качестве внешнего устройства может служить любой объект управления или источник информации (различные датчики, кнопки, исполнительные механизмы, двигатели, реле и т.д.).

Не нашли, что искали? Воспользуйтесь поиском по сайту: ©2015 - 2024 stydopedia.ru Все материалы защищены законодательством РФ.

|