|

|

Микропроцессорные комплектыИ микро-ЭВМ

Микропроцессорные комплекты (МПК) представляют собой единый набор программируемых сверхбольших интегральных схем (СБИС), совместимых по конструктивно-технологическому признаку и предназначенных для построения законченных функциональных устройств. Выпускаемые в настоящее время МПК разделяются на универсальные и специализированные. Универсальные МПК (К580, К584, К586, К588, К589, К1801, К1802, К1804, К1810, К1889) предназначены для решения широкого круга задач в различных отраслях техники. Специализированные МПК (К536, К581, К586, К 1883) ориентированы на решение узкого круга специальных задач. Можно выделить два основных направления использования МПК: - создание законченных функциональных устройств, объединяющих отдельные элементы МПК в единое целое с целью реализации универсальных или узко специализированных задач; - включение отдельных элементов МПК в обычные непрограммируемые устройства с жесткой логикой работы, где они используются в качестве отдельных микросхем наряду с другими непрограммируемыми интегральными схемами (ИС) и служат для реализации ограниченного набора функций. МПК можно использовать как законченные функциональные устройства и для построения на их базе микро-ЭВМ и контроллеров. Контроллером называется устройство, осуществляющее управление автономным объектом по заданному алгоритму. К контроллерам относятся многочисленные цифровые устройства для управления промышленными объектами и процессами, контрольно-измерительными приборами, устройствами хранения и ввода-вывода информации. Для реализации микро-ЭВМ и микроконтроллеров в МПК входят БИС ОЗУ, ПЗУ или ППЗУ, а также специализированные и вспомогательные БИС буферных регистров, магистральных приемопередатчиков, генераторы синхросигналов, формирователи сигналов переноса и др. Структуры микро-ЭВМ и микрошина адреса (А) контроллеров зависят от принципа построения микропроцессоров, на которых они реализуются. МИКРОПРОЦЕССОР СЕРИИ 1821 (Intel 8085A)

Структура микропроцессора К1821ВМ85А Блок регистров Синхронизация и последовательность действий МП Система прерываний

Структура микропроцессора К1821ВМ85А

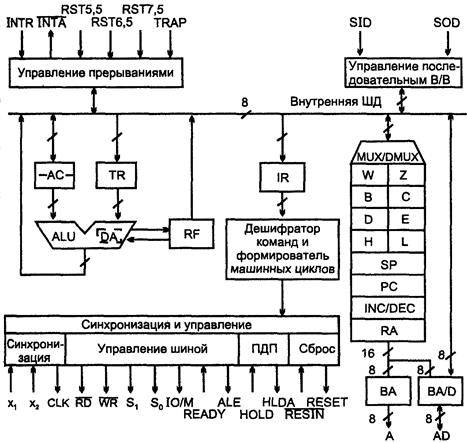

Микропроцессор имеет восьмиразрядную шину данных (внутреннюю), через которую его блоки обмениваются информацией. Структура микропроцессора К1821ВМ85А показана на рис. 5.1.

Рис. 5.1. Структура микропроцессора К 8121 ВМ85А На схеме приняты следующие обозначения: q AC (Accumulator) - регистр-аккумулятор, выполненный на двухступенчатых триггерах и способный хранить одновременно два слова (один из операндов и результат операции); q TR (Temporary Register) - регистр временного хранения одного из операндов; q ALU (Arithmetic-Logic Unit) - арифметико-логическое устройство, выполняющее действия над двумя словами-операндами, подаваемыми на q RF (Register Flags) — регистр флажков, т. е. битов, указывающих признаки результатов арифметических или логических операций, выполненных в АЛУ. Указываются пять признаков: Z (Zero) — нулевой результат, С (Carry) - перенос, AC (Auxiliary Carry) - вспомогательный перенос, S (Sign) - знак, Р (Parity) - четность веса слова. Признак вспомогательного переноса (переноса между младшей и старшей тетрадами восьмиразрядного слова) нужен при выполнении операций в двоично-десятичном коде. Смысл остальных признаков ясен из их наименований. Признаки служат для управления ходом процесса обработки информации.

Блок регистров

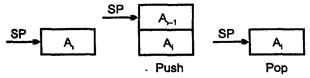

С внутренней шиной данных через мультиплексор связан блок регистров, Регистры W и Z предназначены только для временного хранения данных Регистры В, С, D, E, H, L относятся к регистрам общего назначения, т. к. могут быть использованы по усмотрению программиста. Эти восьмиразрядные регистры могут применяться либо по отдельности, либо в виде пар В-С, D-Е, H-L, играющих роль 16-разрядных регистров. Пары регистров именуются по первым регистрам пары как пары В, D, H. Пара H-L, как правило, используется для размещения в ней адресов при косвенной регистровой адресации. В блоке регистров имеются также 16-разрядные регистры SP и PC. Регистр SP (Stack Pointer) - указатель стека. Стек (магазинная память) удобен для запоминания массива слов, т. к. при этом не требуется адресовать каждое слово отдельно. Слова загружаются в стек в определенном порядке, при считывании также заранее известен порядок их следования. В частности, стек При организации типа LIFO (Last In - First Out) последнее записанное в стек слово при считывании появляется первым. Стек LIFO по порядку записи-считывания подобен стопке тарелок - для использования снимается верхняя, т.е. последняя положенная, затем вторая и т.д. Интересно отметить, что сам термин "стек" произошел именно от обозначения такой стопки. Стек имеет дно и верхушку, направление возрастания номеров ячеек в нем Аппаратно стек реализуется в ОЗУ, где для него выделяется определенная При байтовой организации памяти и занесении в стек содержимого регистровой пары старший байт запоминается по адресу SP-1, а младший - по

Рис. 5.2. Реализация стека в микропроцессорной системе Основное назначение стека - обслуживание прерываний программы и выполнения подпрограмм. Программный счетчик PC (Program Counter) дает адрес команды, и может Регистр команд IR (Instruction Register) принимает из памяти первый байт Блок синхронизации и управления использует выход дешифратора команд и шифратора машинных циклов для синхронизации циклов, генерации сигналов состояния и управления шиной (внешними устройствами микропроцессорной системы). При обмене между МП и памятью или ВУ адрес соответствующей ячейки Буфер адреса ВА с тремя состояниями выхода выдает сигналы старших раз Буфер шины адресов/данных BA/D с тремя состояниями выхода передает на шину A/D с разделением во времени младший байт адреса или байт данных. Внутренняя восьмиразрядная шина данных передает байты между различными внутренними регистрами или обменивается с другими модулями МПС через мультиплексируемую шину адресов/данных. Назначение блоков управления прерыванием и последовательным вводом-

Не нашли, что искали? Воспользуйтесь поиском по сайту: ©2015 - 2024 stydopedia.ru Все материалы защищены законодательством РФ.

|